## HP 8340A SYNTHESIZED SWEEPER

10 MHz to 26.5 GHz

Model 8340A Table of Contents

#### **VOLUME 4 TABLES**

| Table          | Pa                              | ge | Table | Page                                 |

|----------------|---------------------------------|----|-------|--------------------------------------|

| 8I-1.          | Function Select Truth Table 8-7 | 78 | 8J-3. | A52 Positive Regulator, Regulated    |

| 8I <b>-</b> 2. | HMTR and HINT Functions 8-79    | 90 |       | Supply Limits 8-916                  |

| 8J-1.          | A35 Rectifier, Regulated        |    | 8J-4. | A53 Negative Regulator, Regulated    |

|                | Supply Limit 8-89               | 92 |       | Supply Limits 8-934                  |

| 8J-2.          | Power Supply Output Current     |    | 8J-5. | A56 −15V Supply, Regulated           |

|                | Capability8-9                   | 01 |       | Supply Limit 8-934                   |

|                | •                               |    | 8J-6. | Power Supply Destination Chart 8-941 |

#### SAFETY CONSIDERATIONS

#### **GENERAL**

This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation. This product has been designed and tested in accordance with international standards.

#### **SAFETY SYMBOLS**

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual (refer to Table of Contents).

Indicates hazardous voltages.

Indicates earth (ground) terminal.

#### WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

### CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

#### **SAFETY EARTH GROUND**

This is a Safety Class I product (provided with a protective earthing terminal). An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

#### BEFORE APPLYING POWER

Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an autotransformer, make sure the common terminal is connected to the neutral (grounded) side of mains supply.

#### **SERVICING**

#### WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

# REFERENCE GUIDE TO SERVICE DOCUMENTATION

|                           | //                                                                                         |                       |     | 7                   |       | 7          | Vol | ume     | 3 | 7            | Volume |

|---------------------------|--------------------------------------------------------------------------------------------|-----------------------|-----|---------------------|-------|------------|-----|---------|---|--------------|--------|

|                           | Description                                                                                |                       | /   | /                   | / _   | 7          |     |         |   | _            |        |

|                           | Description                                                                                | /                     | 1   | W. Mill             |       | \$<br>\$\s | 0   |         |   |              |        |

| 1                         | 3/                                                                                         |                       | 4   | Se Mill dion        |       | (G<br>2) 2 |     |         |   |              |        |

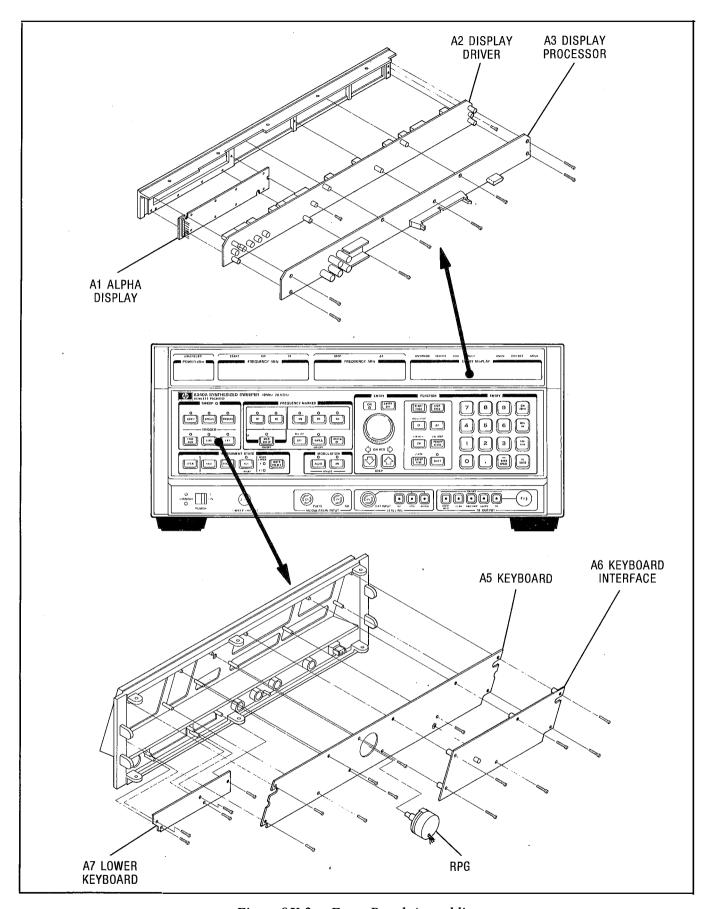

| A1<br>A2                  | Alpha Display<br>Display Driver                                                            | 33                    |     |                     |       |            |     | •       |   | <i>,</i> ,   |        |

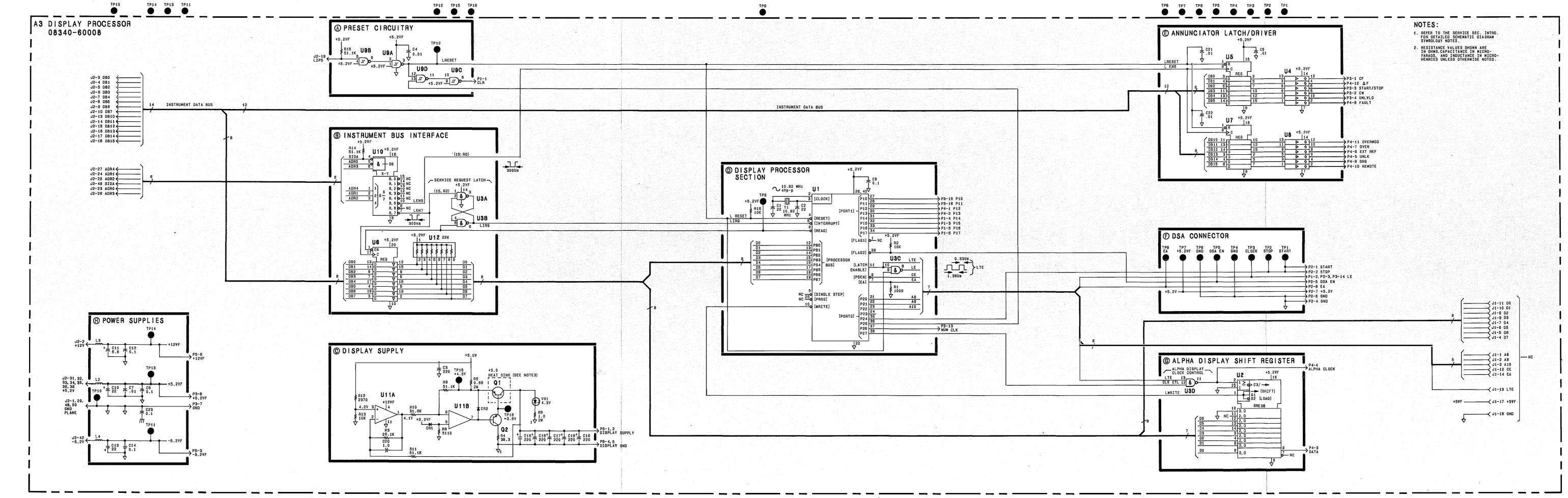

| A3<br>A4                  | Display Processor<br>Not Assigned<br>Keyboard                                              | 33<br>-<br>35         |     |                     |       | ,          |     | •       |   |              |        |

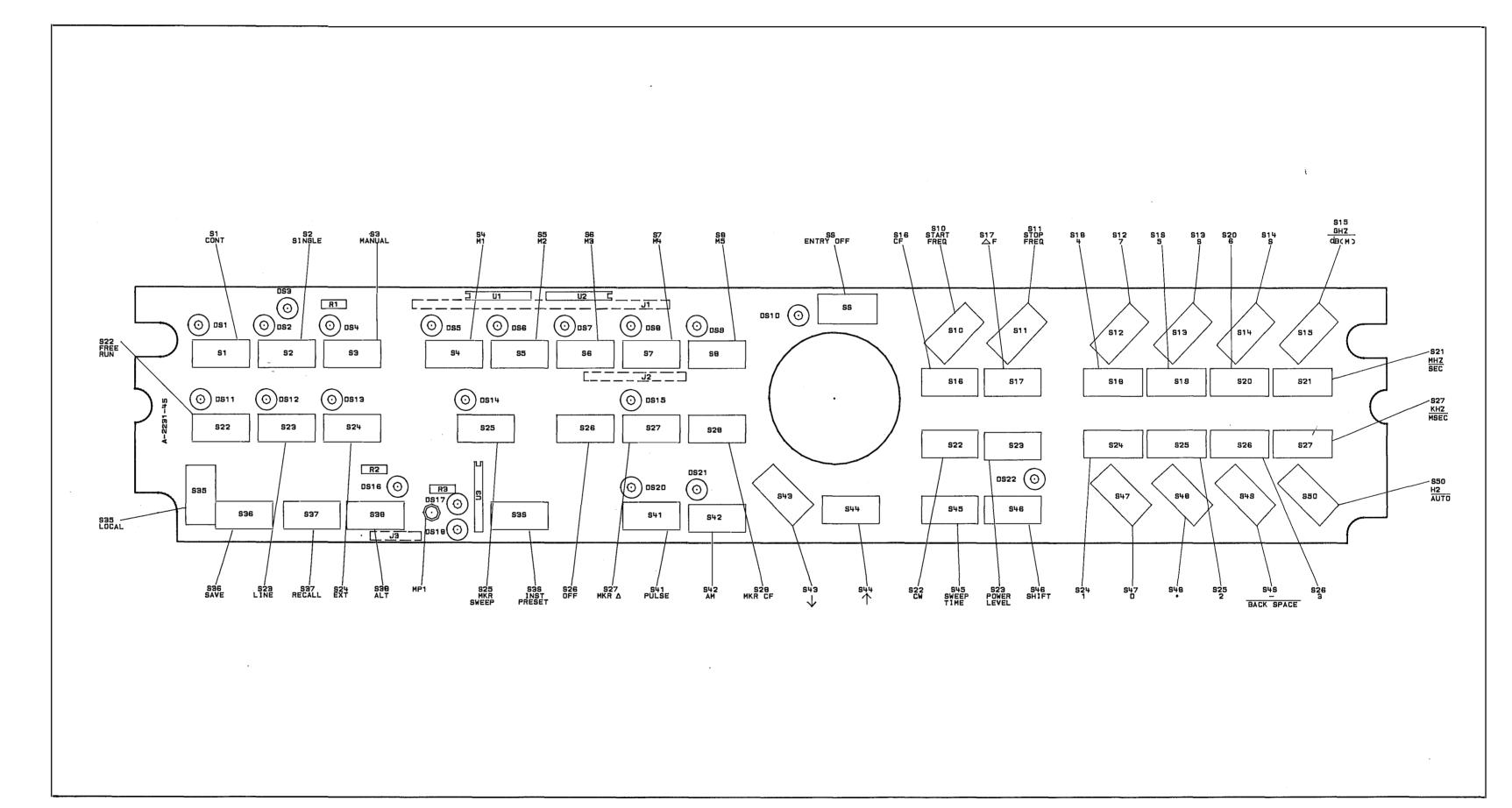

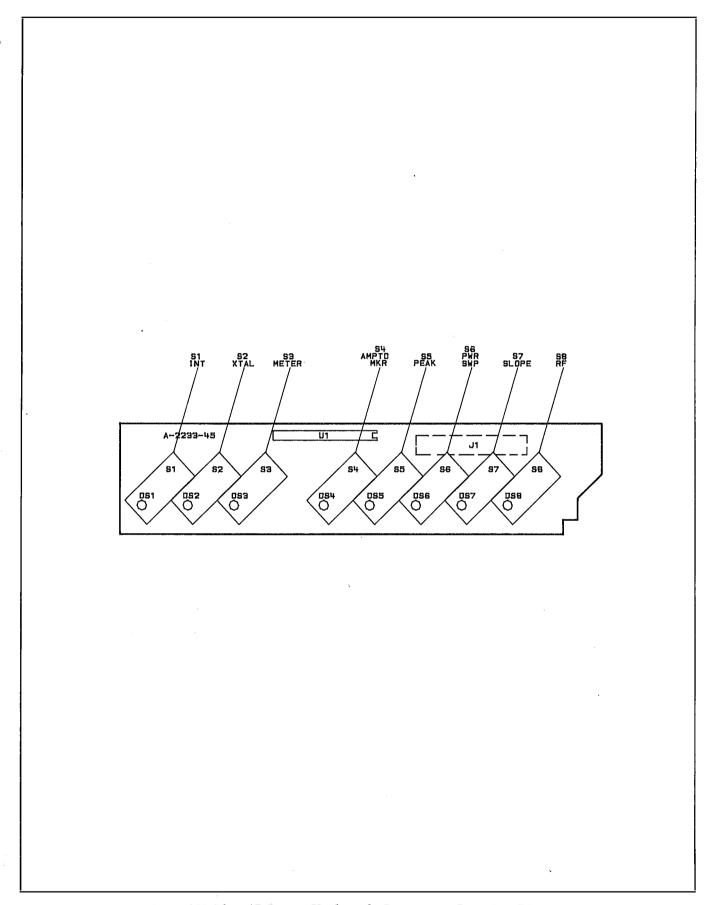

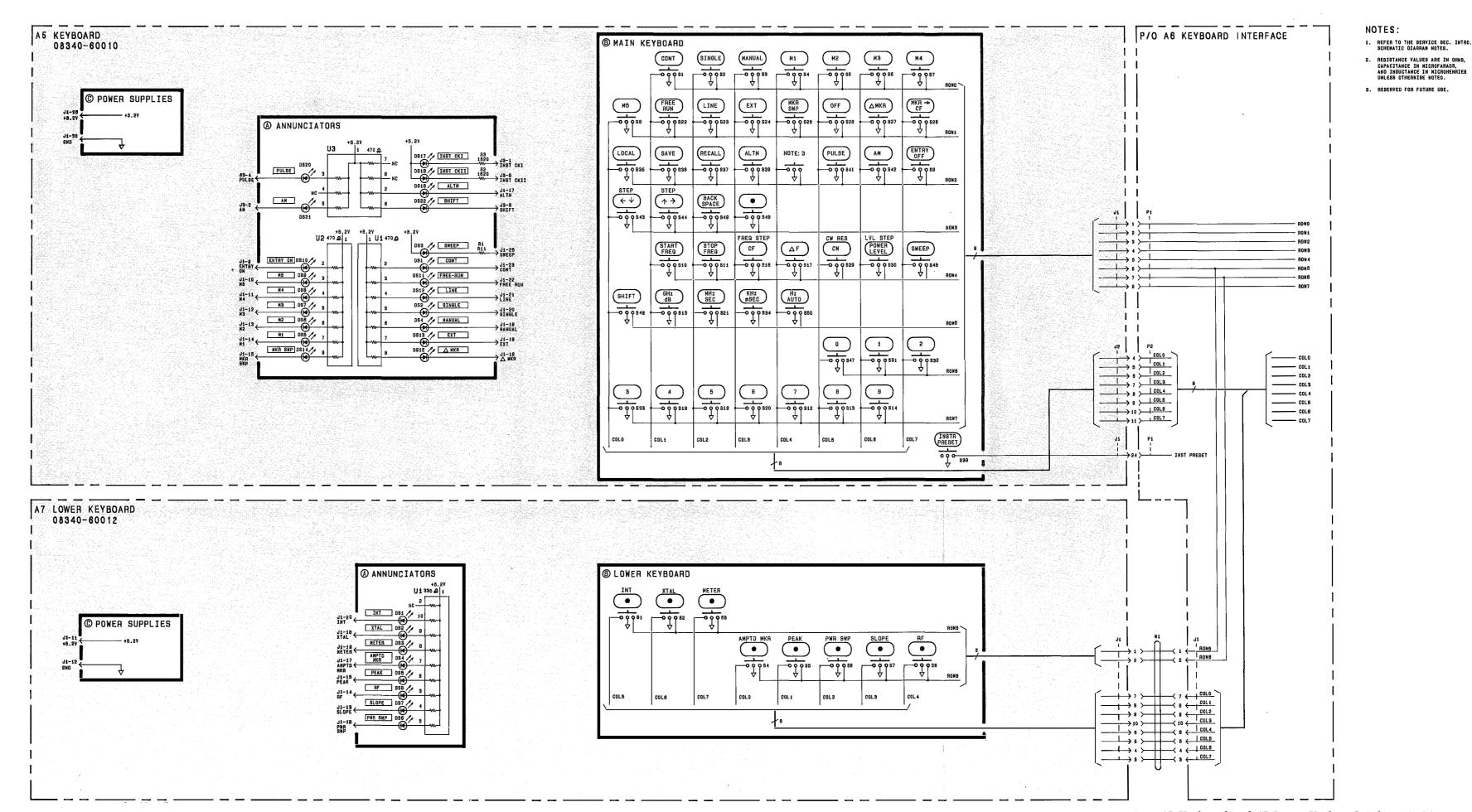

| A5<br>A6<br>A7            | Keyboard Interface<br>Lower Keyboard                                                       | 35<br>35              |     |                     |       |            |     | •       |   |              |        |

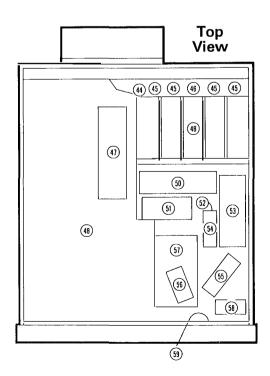

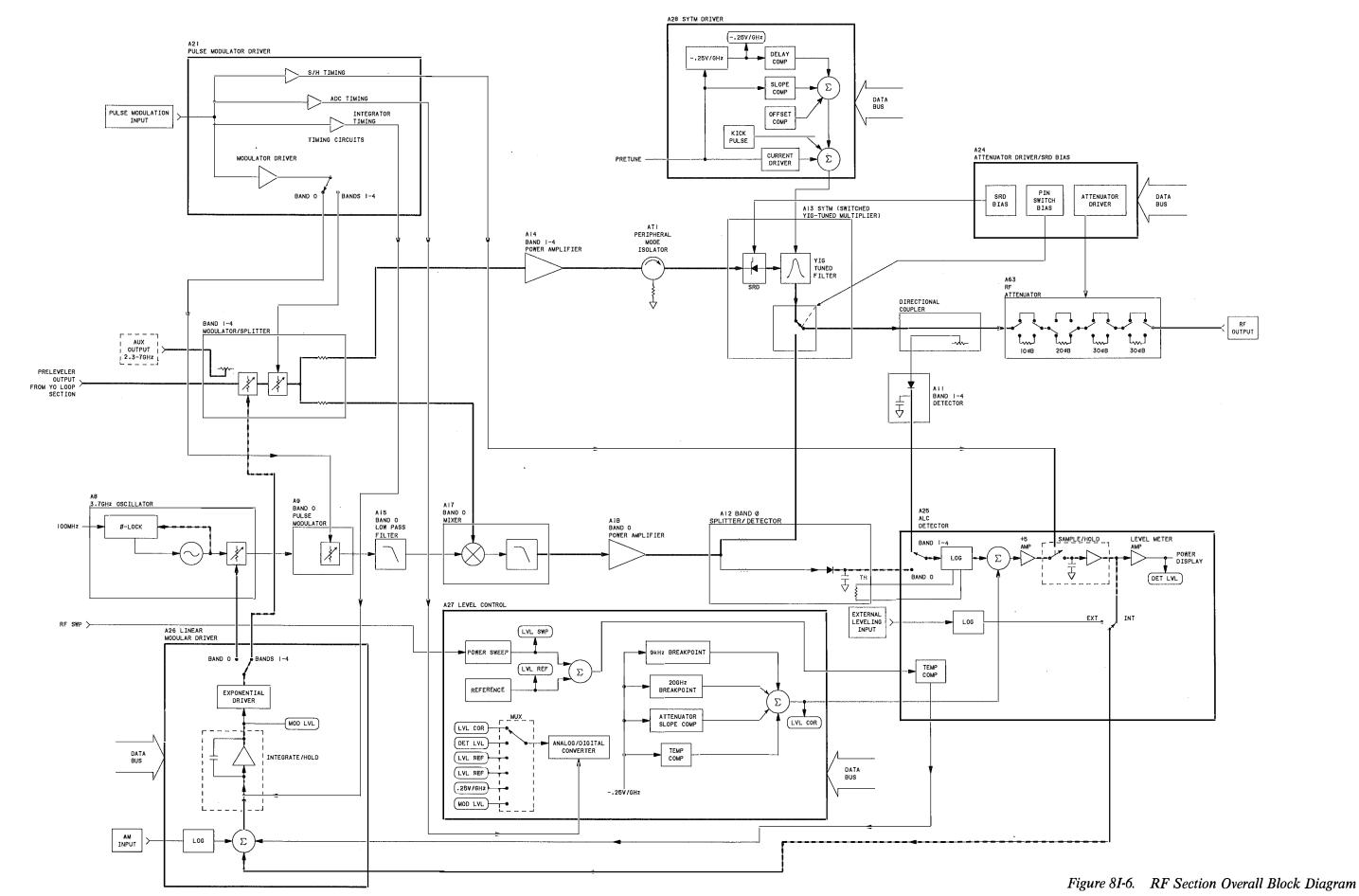

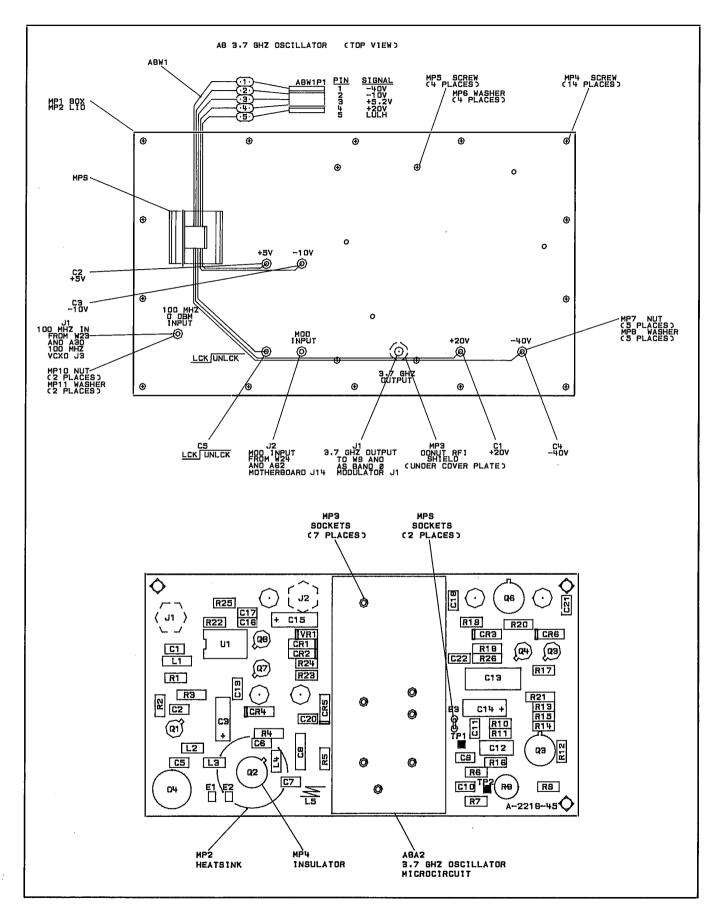

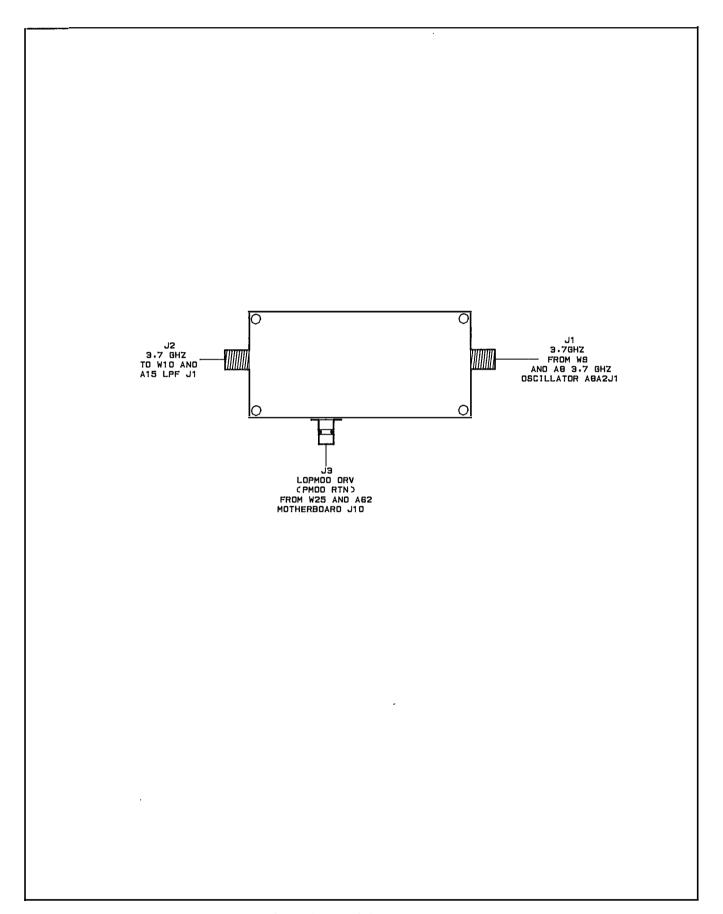

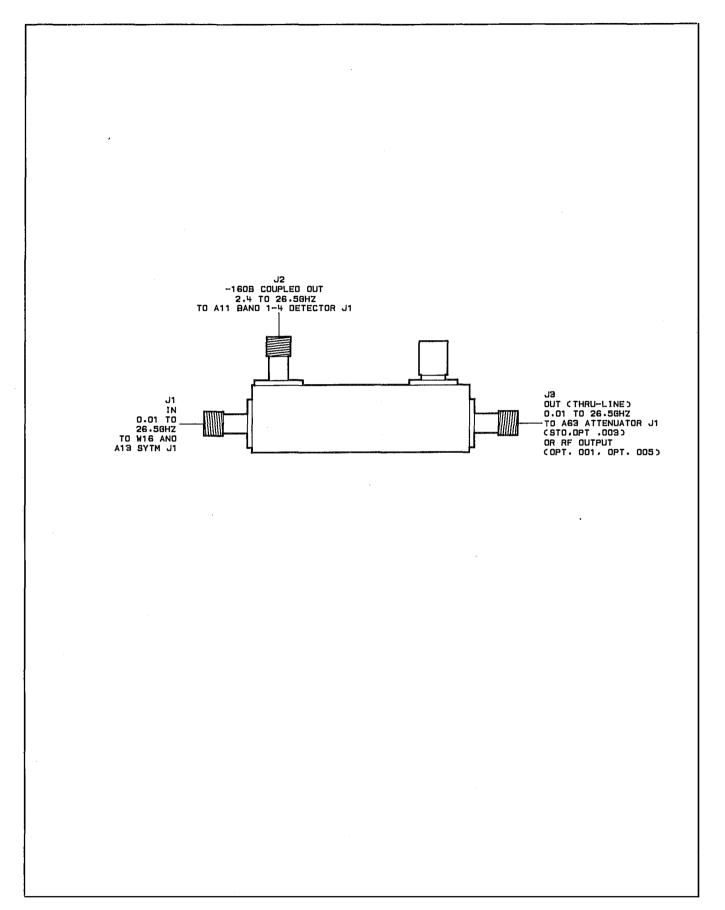

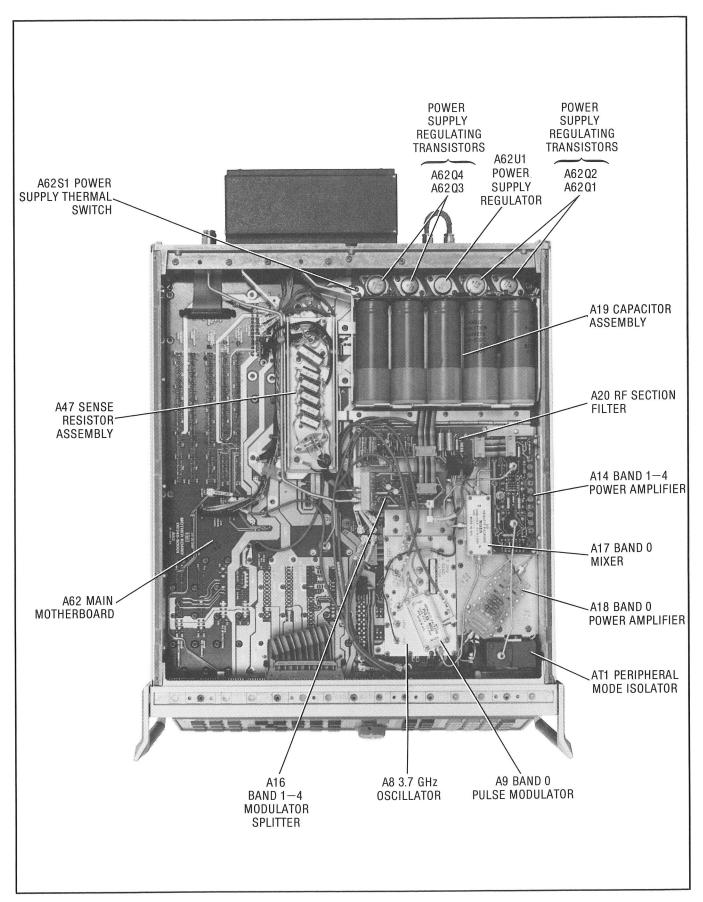

| A8<br>A9.<br>A10          | 3.7 GHz Óscillator  Band O Pulse Modulator  Directional Coupler                            | 57<br>56<br>32        |     |                     |       |            |     |         | • |              |        |

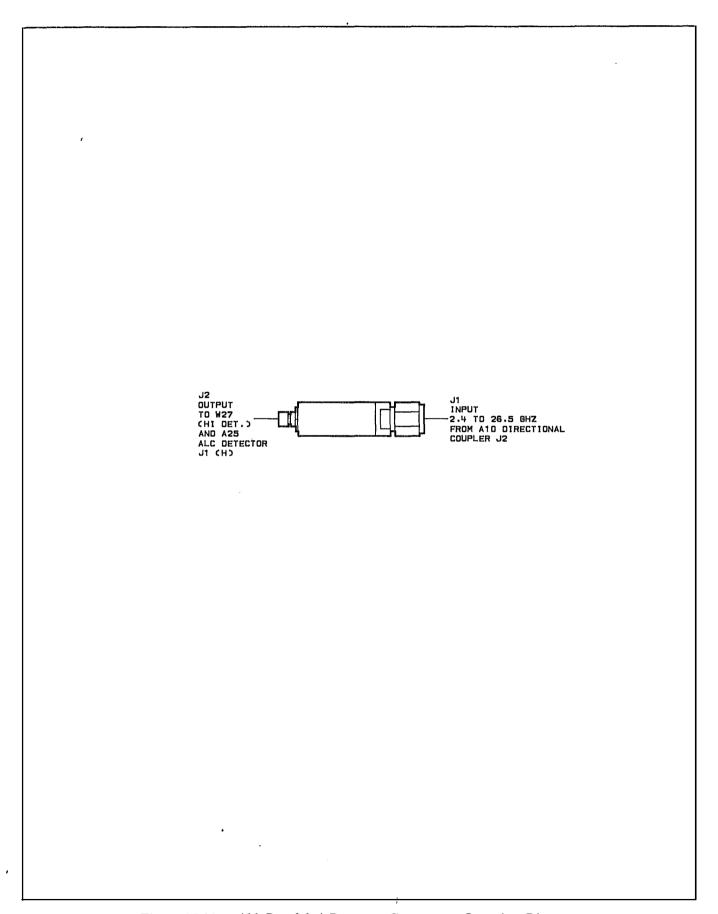

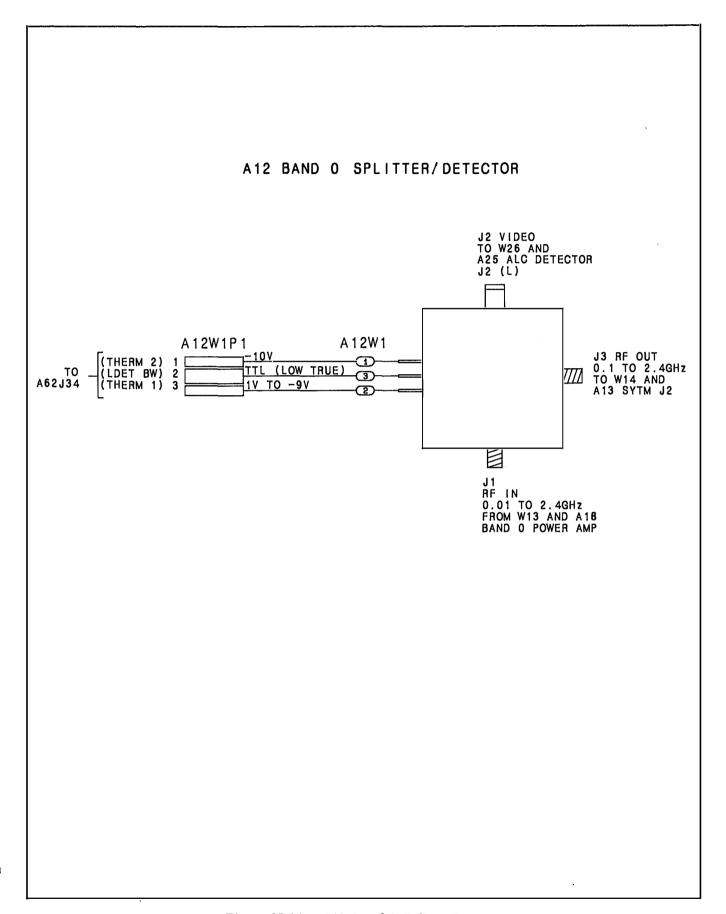

| A11<br>A12                | Band 1-4 Detector<br>Band 0 Splitter/Detector                                              | 31<br>34<br>30        |     |                     |       |            |     |         | • |              |        |

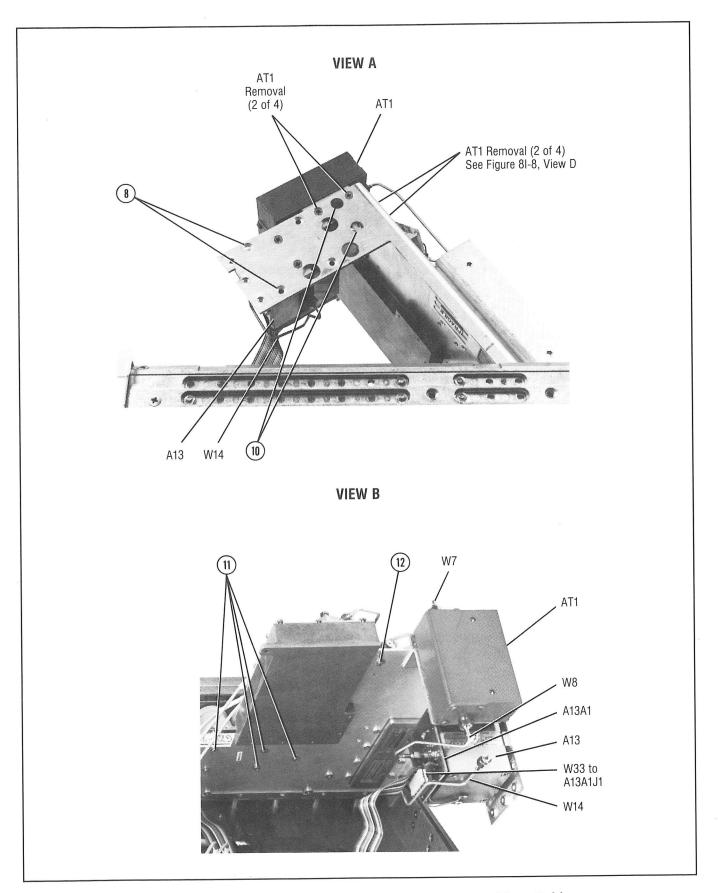

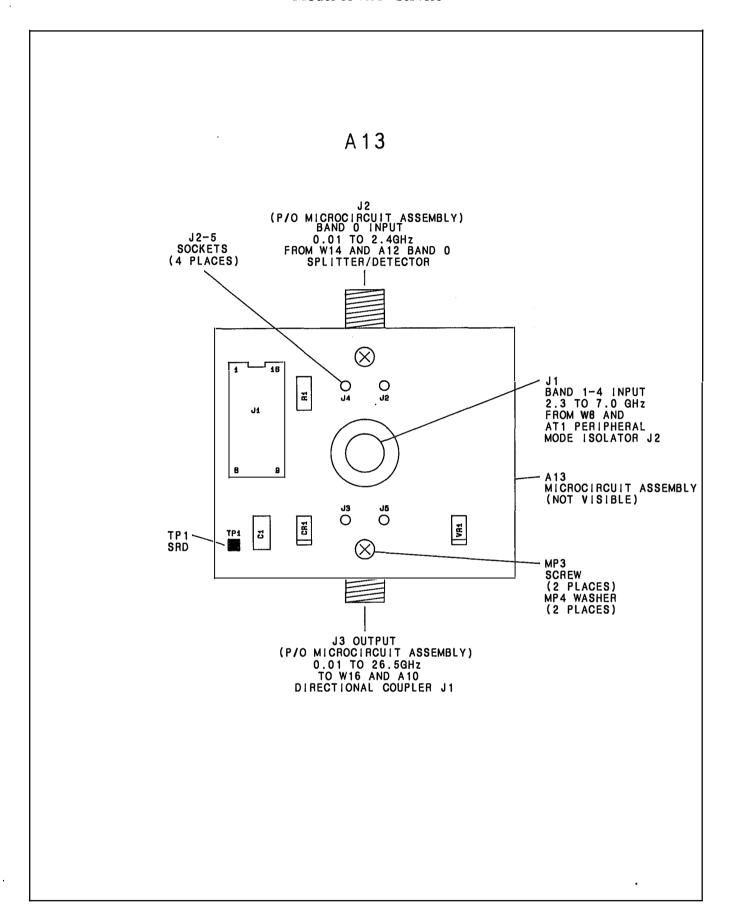

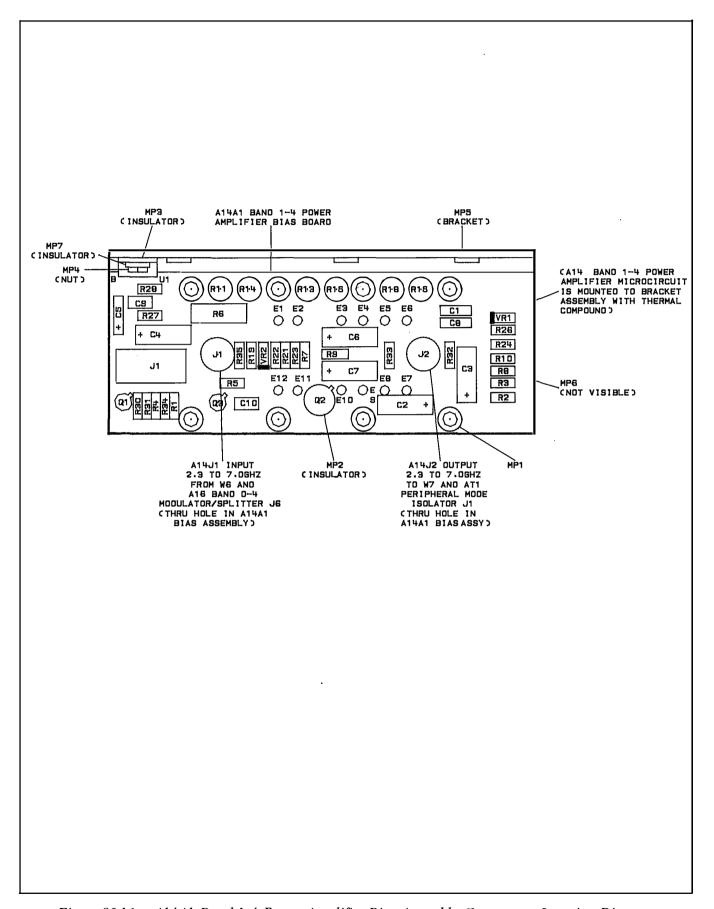

| A13<br>A14<br>A15         | SYTM (Switched YIG Tuned Multiplier)<br>Band 1-4 Power Amplifier<br>Band 0 Low Pass Filter | 53<br>52              |     |                     |       | ٠          |     |         | • |              |        |

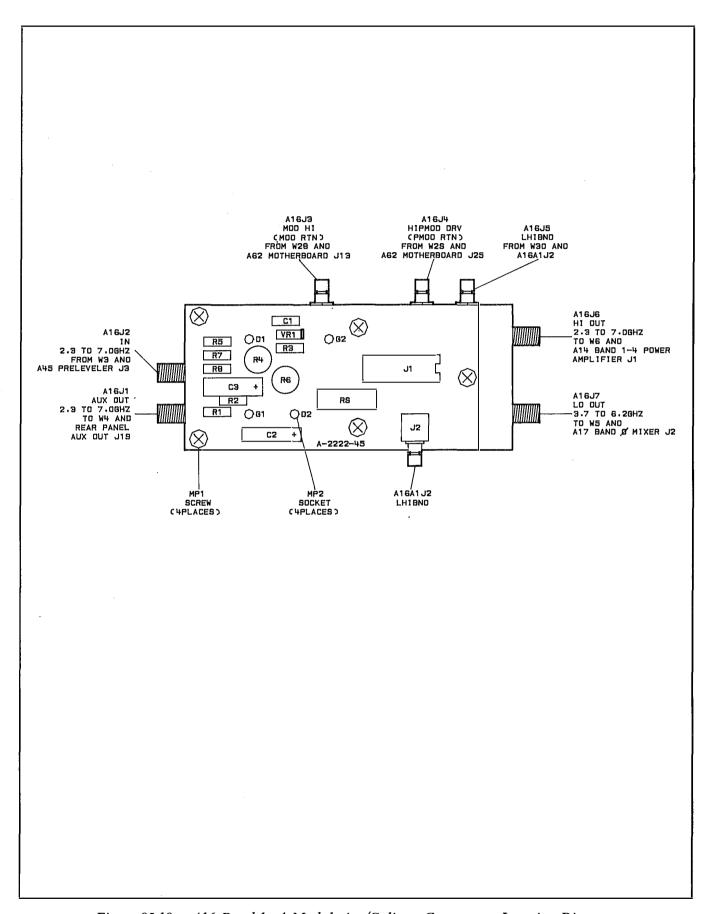

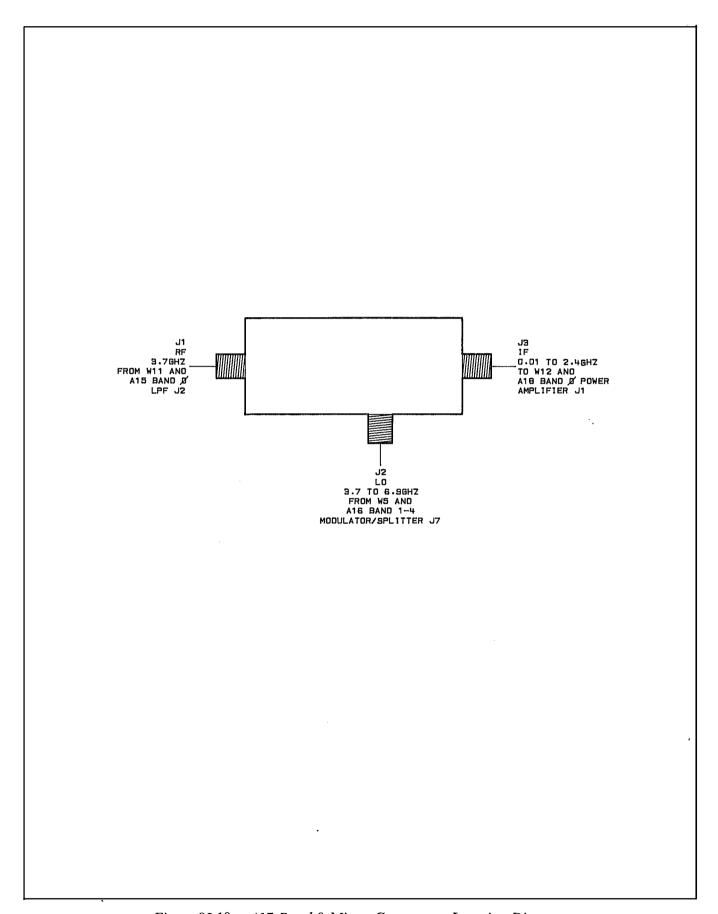

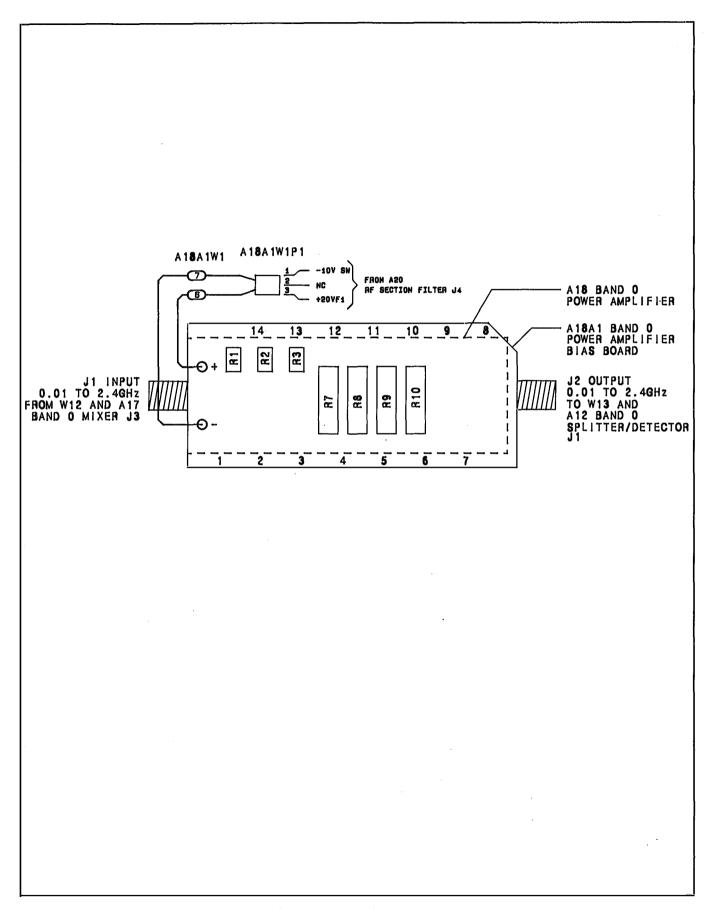

| A16<br>A17<br>A18         | Band 1-4 Modulator/Splitter Band O Mixer Band O Power Amplifier                            | 51<br>54<br>55        |     |                     |       | Jan.       |     |         | • |              |        |

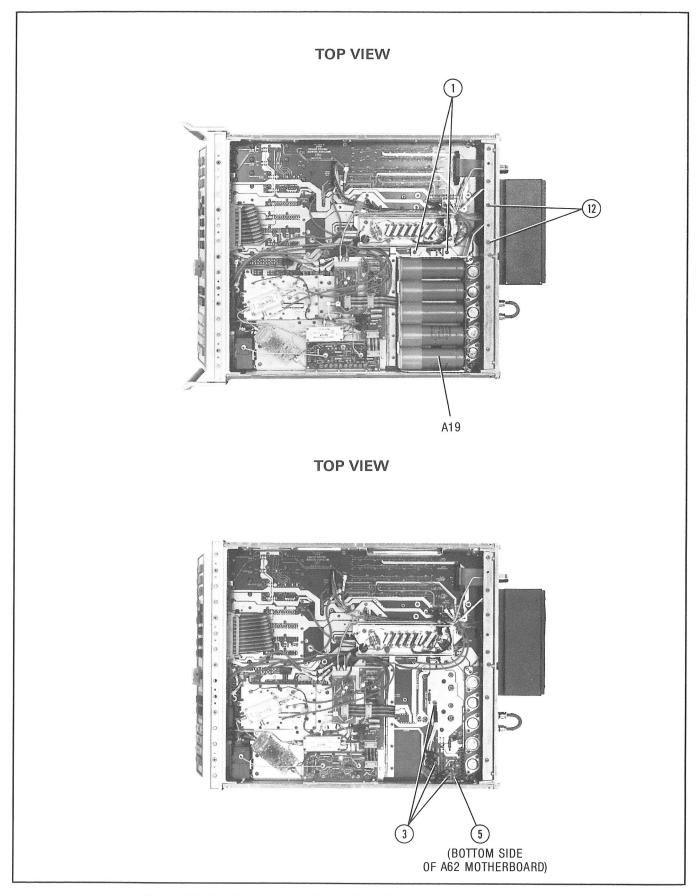

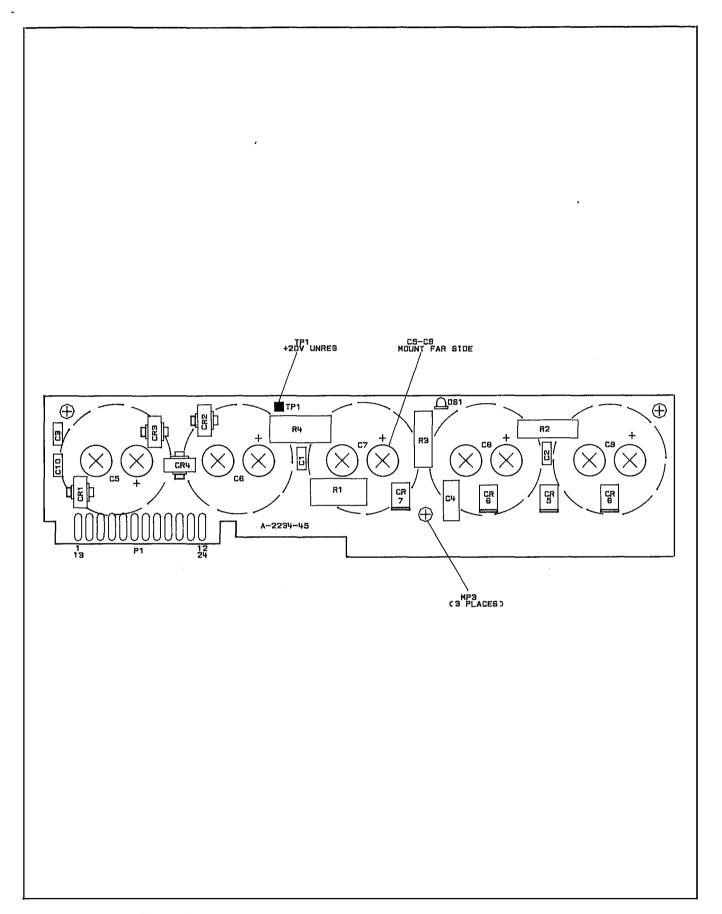

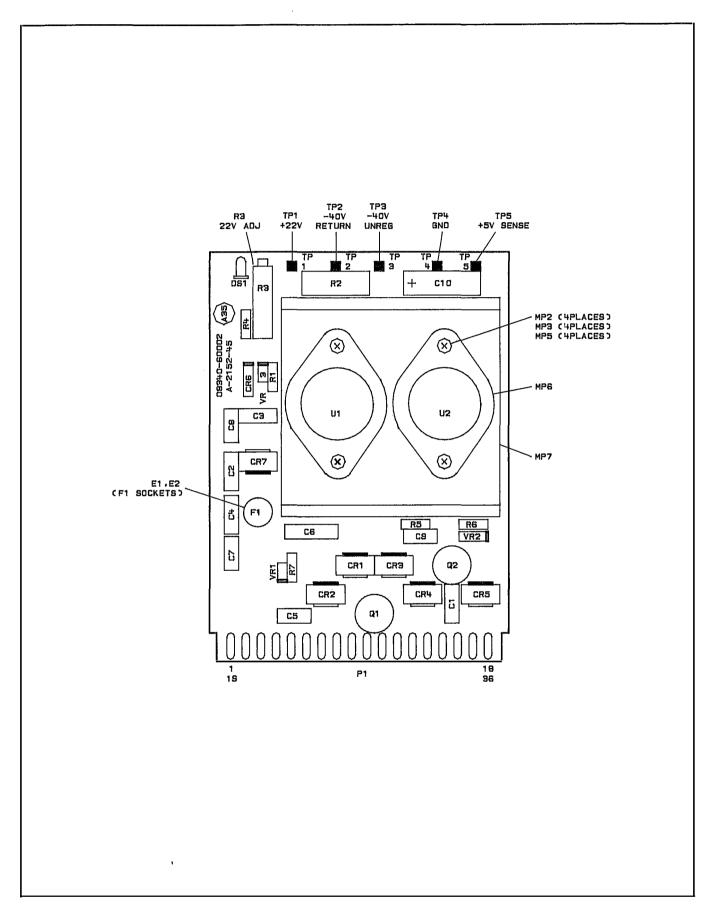

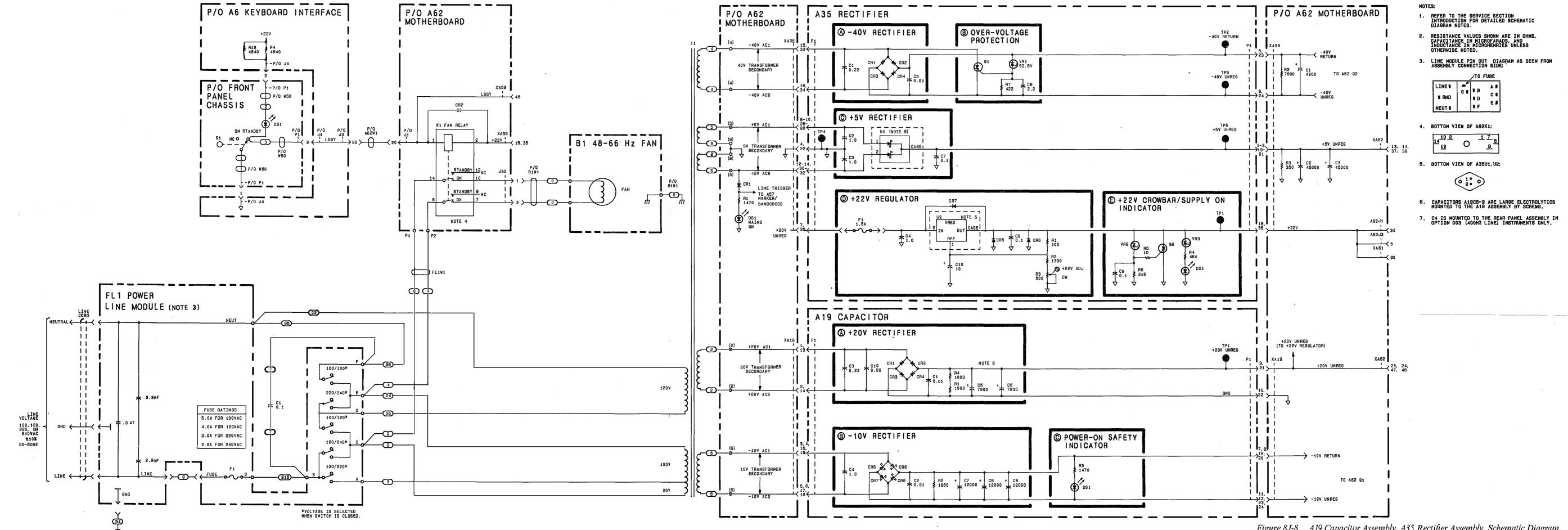

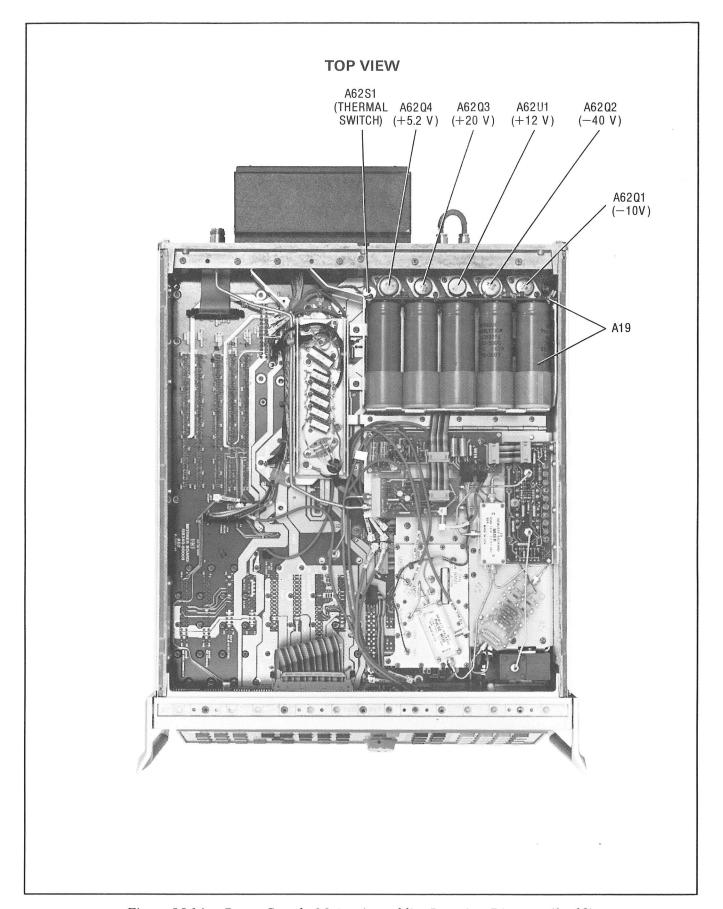

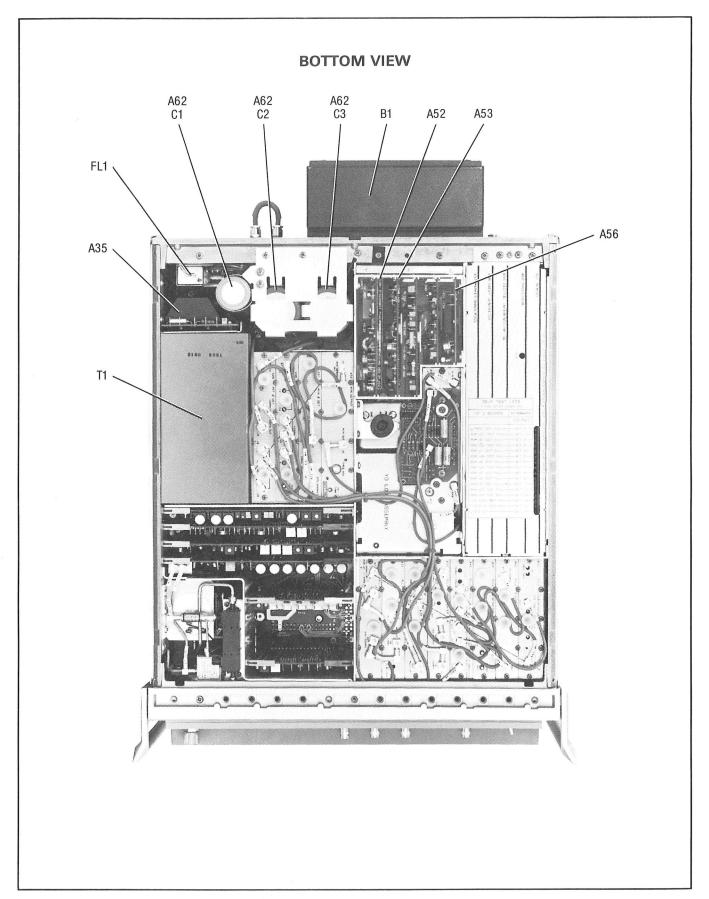

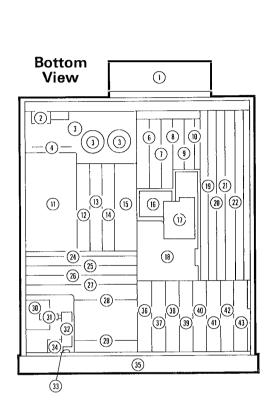

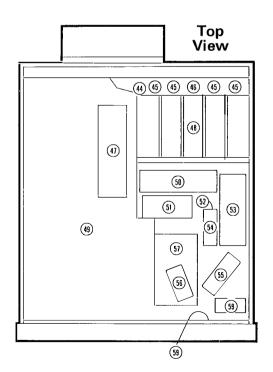

| A19                       | Capacitor Assembly                                                                         | 60<br>48              |     |                     |       |            |     |         | • | •            |        |

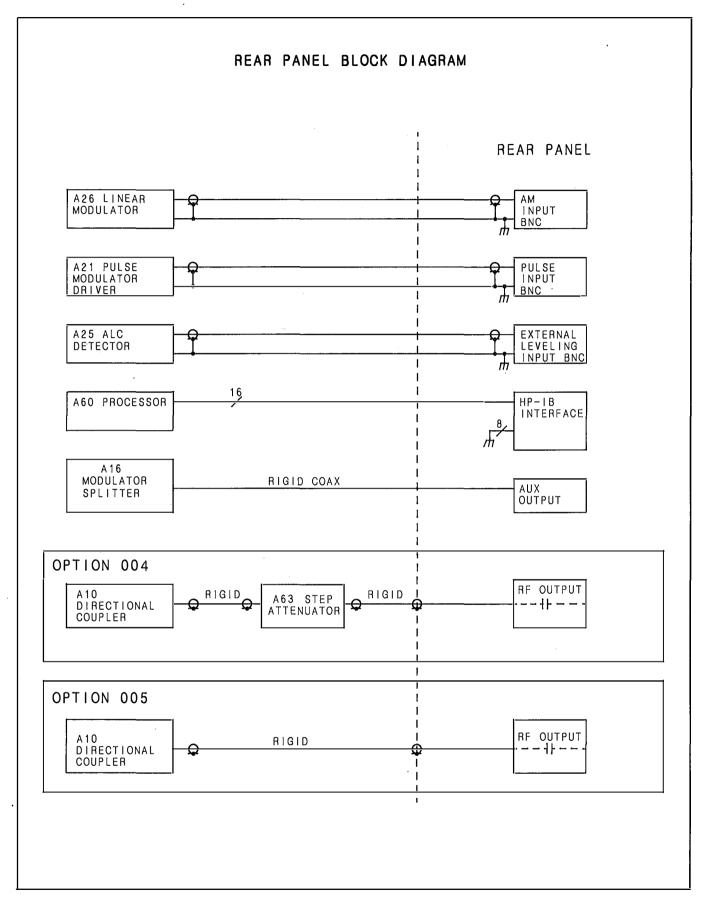

| A20<br>A21<br>A22         | RF Section Filter Pulse Modulator Driver Not Assigned                                      | 50<br>29<br>-         |     |                     |       |            |     | ,       | • |              |        |

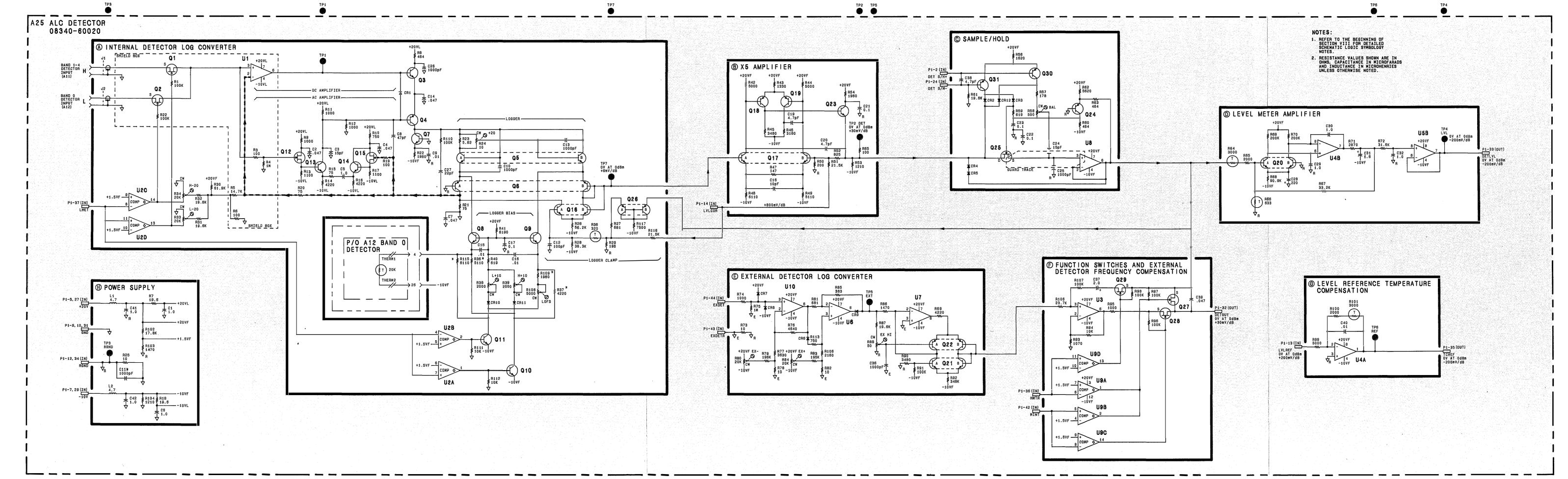

| A23<br>A24 :<br>A25       | Not Assigned Attenuator Driver/SRD Bias ALC Detector                                       | 28<br>27              |     |                     |       |            |     |         | • |              |        |

| A26<br>A27                | Linear Modulator<br>Level Control                                                          | 26<br>25              |     |                     |       |            |     |         | • |              |        |

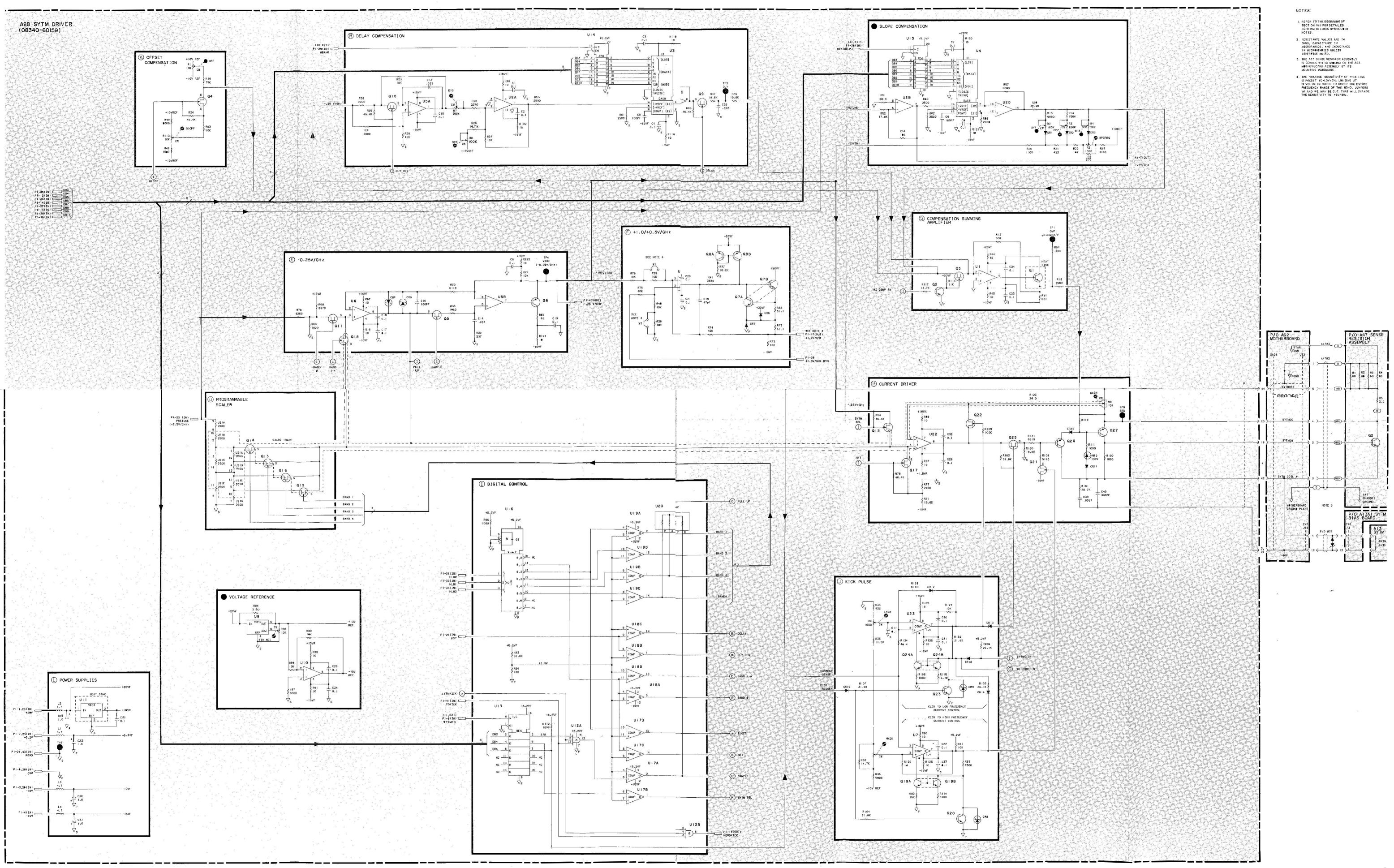

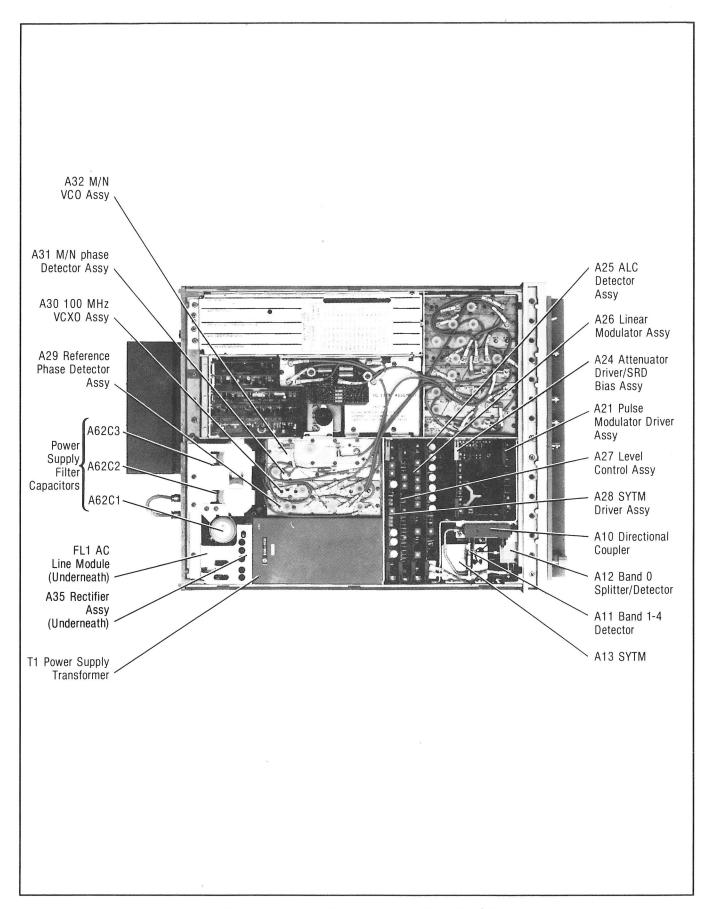

| A28<br>A29<br>A30         | SYTM Driver Reference Phase Detector 100 MHz VCXO (Voltage Controlled Crystal Osc.)        | 24<br>12<br>13        | •   |                     |       |            |     |         | • |              |        |

| A31<br>A32<br>A33         | M/N Phase Detector M/N VCO (Voltage Controlled Osc.) M/N Output                            | 14<br>15<br>15        | •   |                     |       |            |     |         |   |              |        |

| A34<br>A35                | Reference-M/N Motherboard<br>Rectifier                                                     | . 5<br>4              | •   |                     |       |            |     |         |   | •            |        |

| A36<br>A37<br>A38         | PLL1 VCO (Voltage Controlled Osc.)<br>PLL1 Divider<br>PLL1 IF                              | 36<br>37<br>38        |     | •                   |       |            |     |         |   |              |        |

| A39<br>A40<br>A41         | PLL3 Upconverter PLL2 VCO (Voltage Controlled Osc.) PLL2 Phase Detector                    | 39<br>40<br>41        |     | •                   |       |            |     |         |   |              |        |

| A42<br>A43                | PLL2 Divider<br>PLL2 Discriminator                                                         | 42<br>43              |     | •                   |       |            |     |         |   |              |        |

| A44<br>A45<br>A46         | YIG Oscillator (YO) Directional Coupler 7 GHz Low Pass Filter                              | 18<br>18<br>18        |     |                     |       |            |     |         |   |              |        |

| A47                       | Sense Resistor Assembly (YO circuit) (SYTM circuit) YO Loop Sampler                        | 47<br>47<br>18        |     | naega en c          | •     | 0.55250    |     |         |   | 200          |        |

| A49<br>A50                | YO Loop Phase/Detector<br>YO Loop Interconnect                                             | 18<br>17<br>16        |     |                     | •     |            |     |         |   |              |        |

| A51<br>A52<br>A53         | Reference Oscillator Positive Regulator Negative Regulator                                 | 6<br>7                | 998 |                     |       | \$4510ii   |     |         |   | •            |        |

| A54<br>A55<br>A56         | YO Pretune/Delay Compensation YO Driver - 15V Regulator                                    | 8<br>9<br>10          |     |                     | •     |            |     | 1800    |   | P <b>a</b> s |        |

| A57<br>A58                | Market/Bandcross<br>Sweep Generator<br>Digital Interface                                   | 19<br>20<br>21        |     |                     |       |            | •   |         |   |              |        |

| A59 4 A60<br>A61          | Processor<br>Not Assigned                                                                  | 22<br>23              |     | 7413014<br>100 pt 1 |       |            | •   | I HAM   |   |              |        |

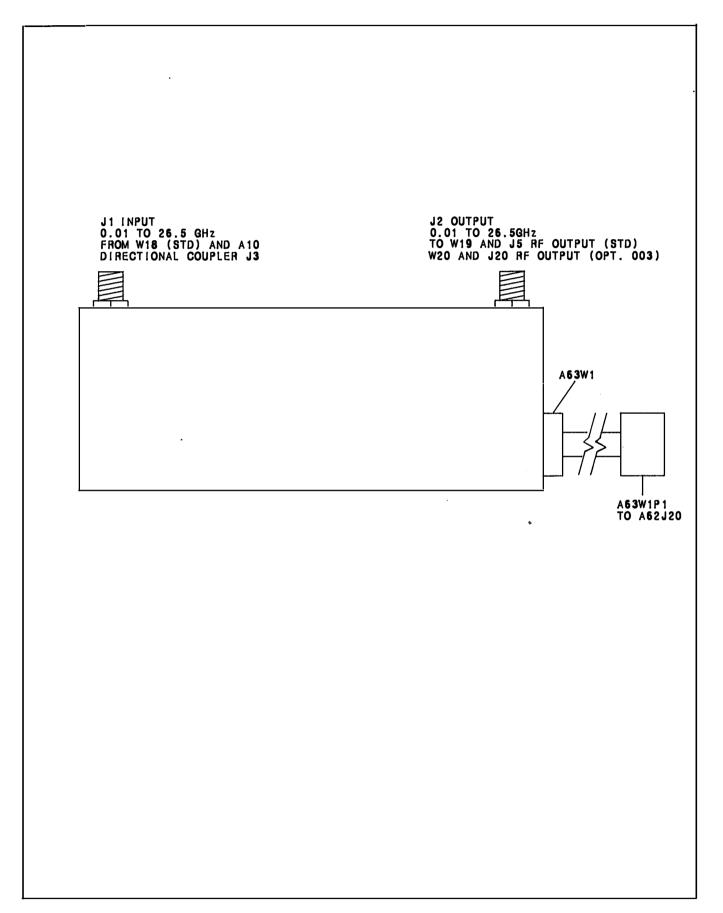

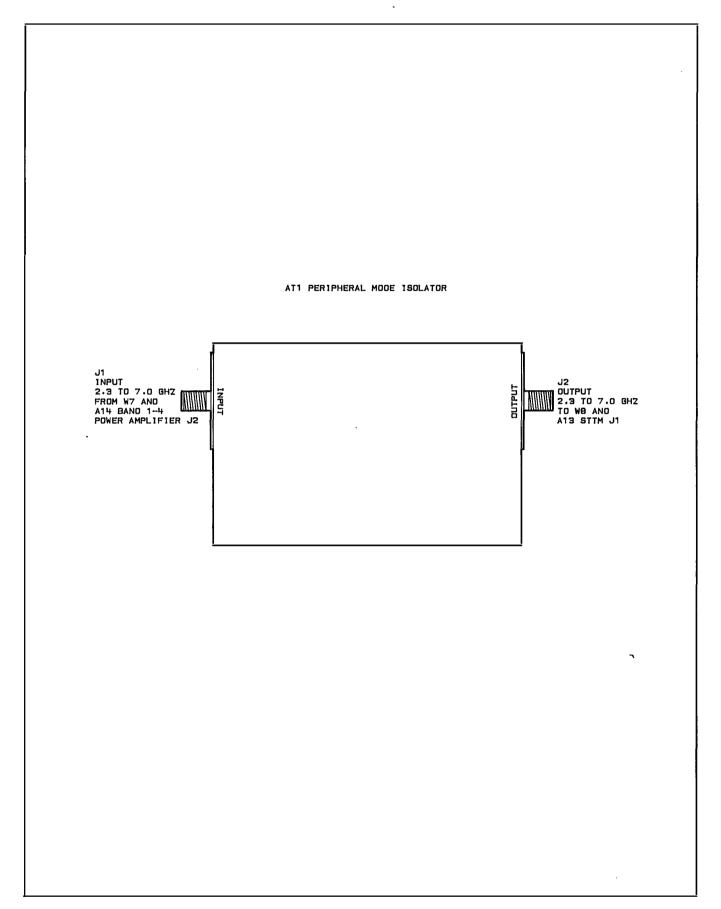

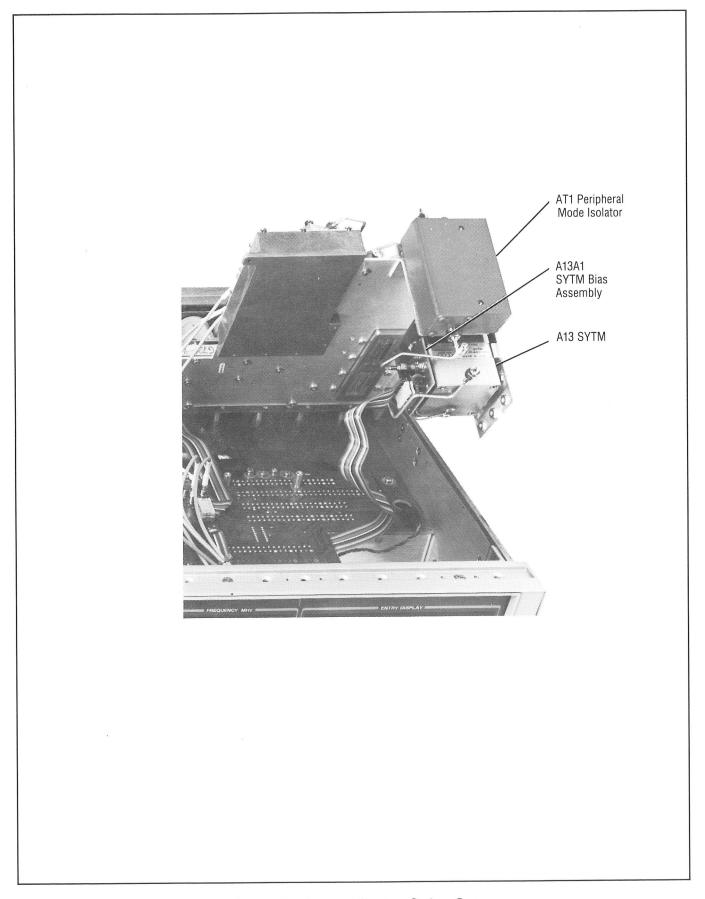

| A62<br>A63<br>AT1         | Motherboard<br>90 dB RF Attenuator<br>Peripheral Mode Isolator                             | 49<br>59<br><b>58</b> |     | wii:                | ya.a. |            |     | 3612    | • | SH           |        |

| AT2<br>81                 | 15 dB Attenuator<br>Fan Assembly                                                           | = 18<br>- 1           |     |                     | •     |            |     |         |   | •            |        |

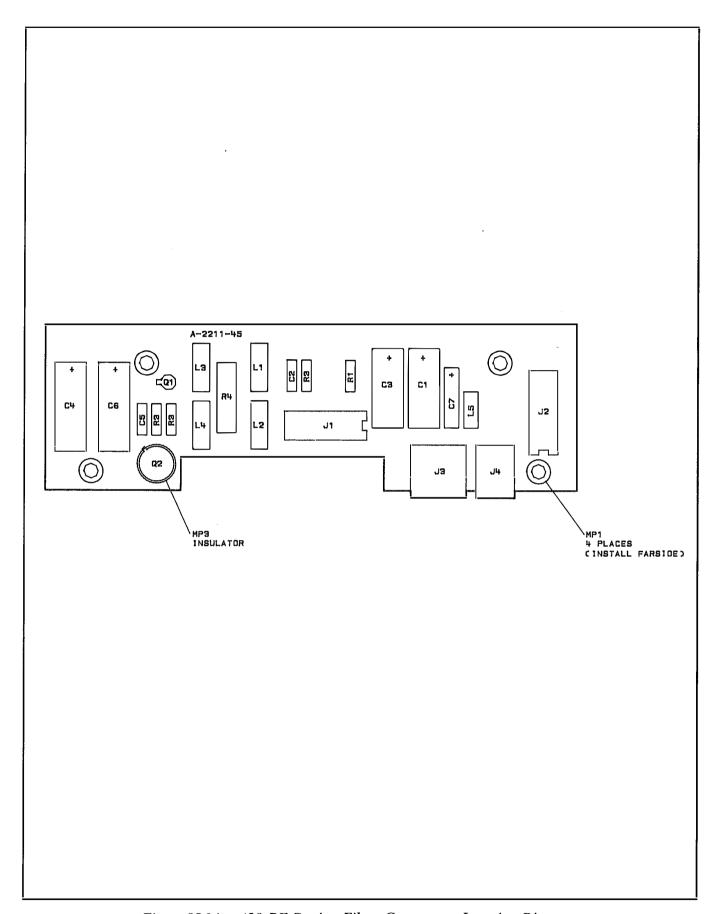

| A62C1-3<br>FL1<br>A62Q1-4 | Power Supply Filter Capacitors  AC Line Module Power Supply Regulating Transistors         | 2<br>45               | 70  |                     |       |            |     | Paris - |   | •            |        |

| A62S1<br>T1<br>A62U1      | Power Supply Thermal Switch<br>Power Supply Transformer<br>Power Supply Regulator          | 44<br>11<br>46        |     |                     |       |            |     |         |   | •            |        |

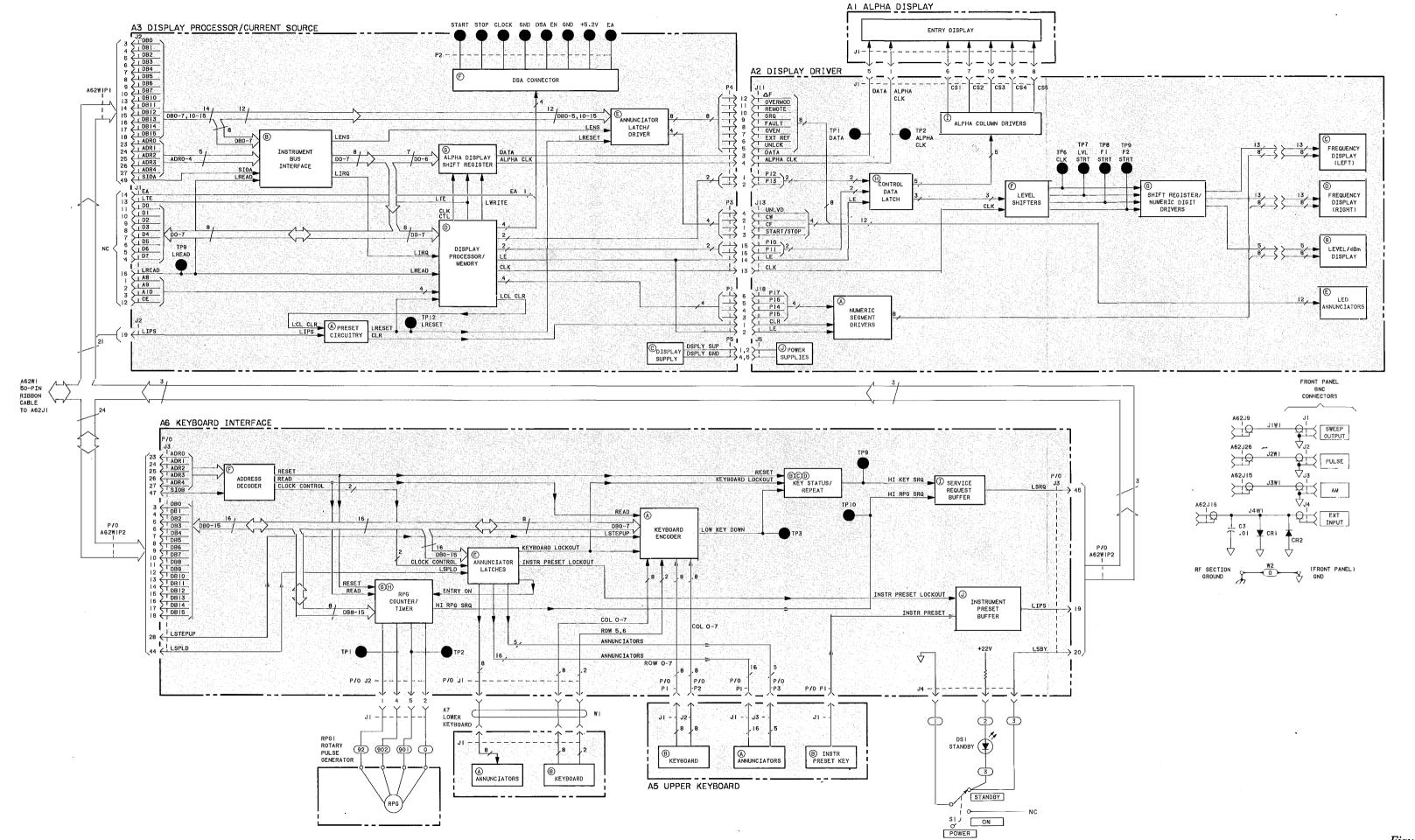

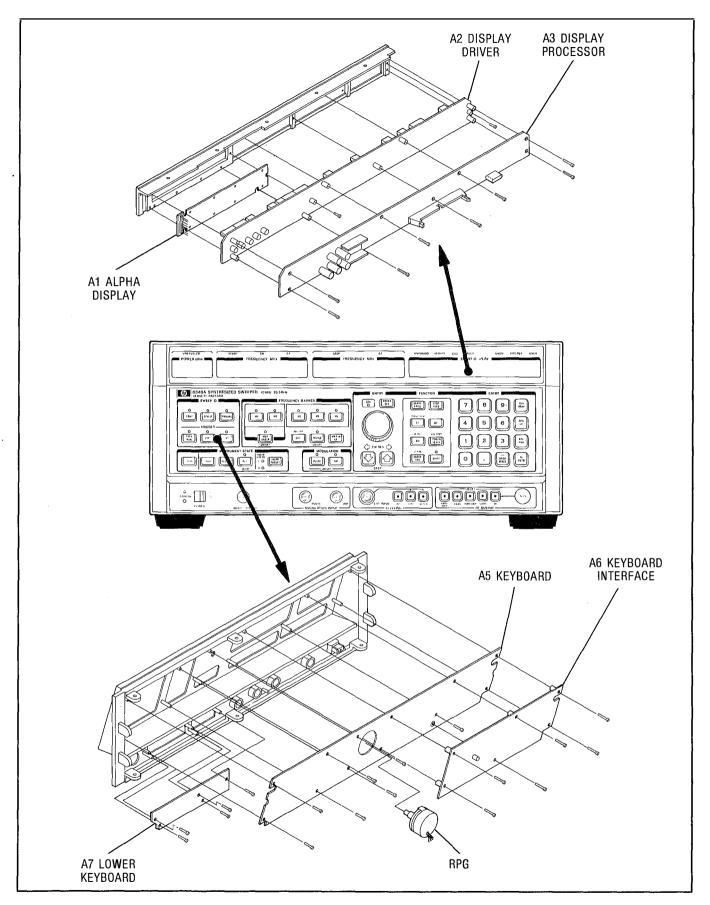

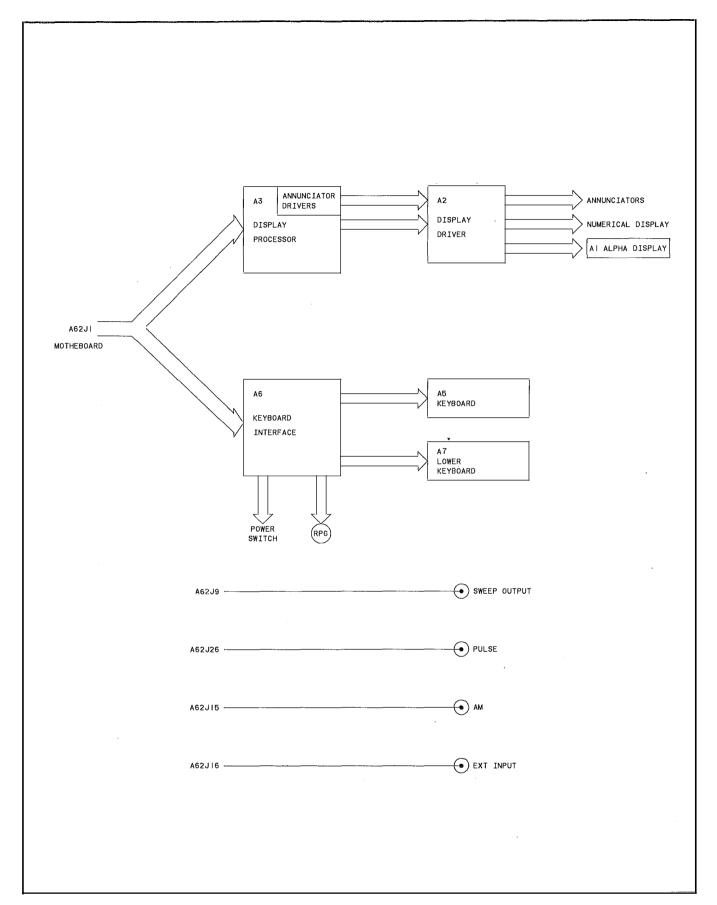

#### CONTROLLER SECTION G

#### INTRODUCTION

#### THEORY OF OPERATION

Controller Section — Overall Description Processor Assembly Description Digital Interface Assembly Description Marker/Bandcross Assembly Description

#### TROUBLESHOOTING TO ASSEMBLY LEVEL

#### **REPAIR PROCEDURES**

Simplified Block Diagram Troubleshooting Block Diagram

#### INDIVIDUAL ASSEMBLY SERVICE SECTIONS

A57 Marker/Bandcross A59 Digital Interface A60 Processor

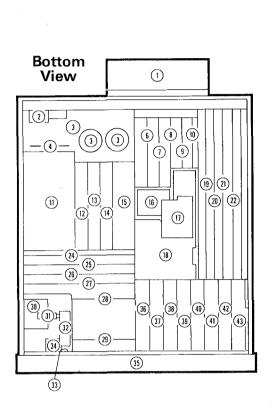

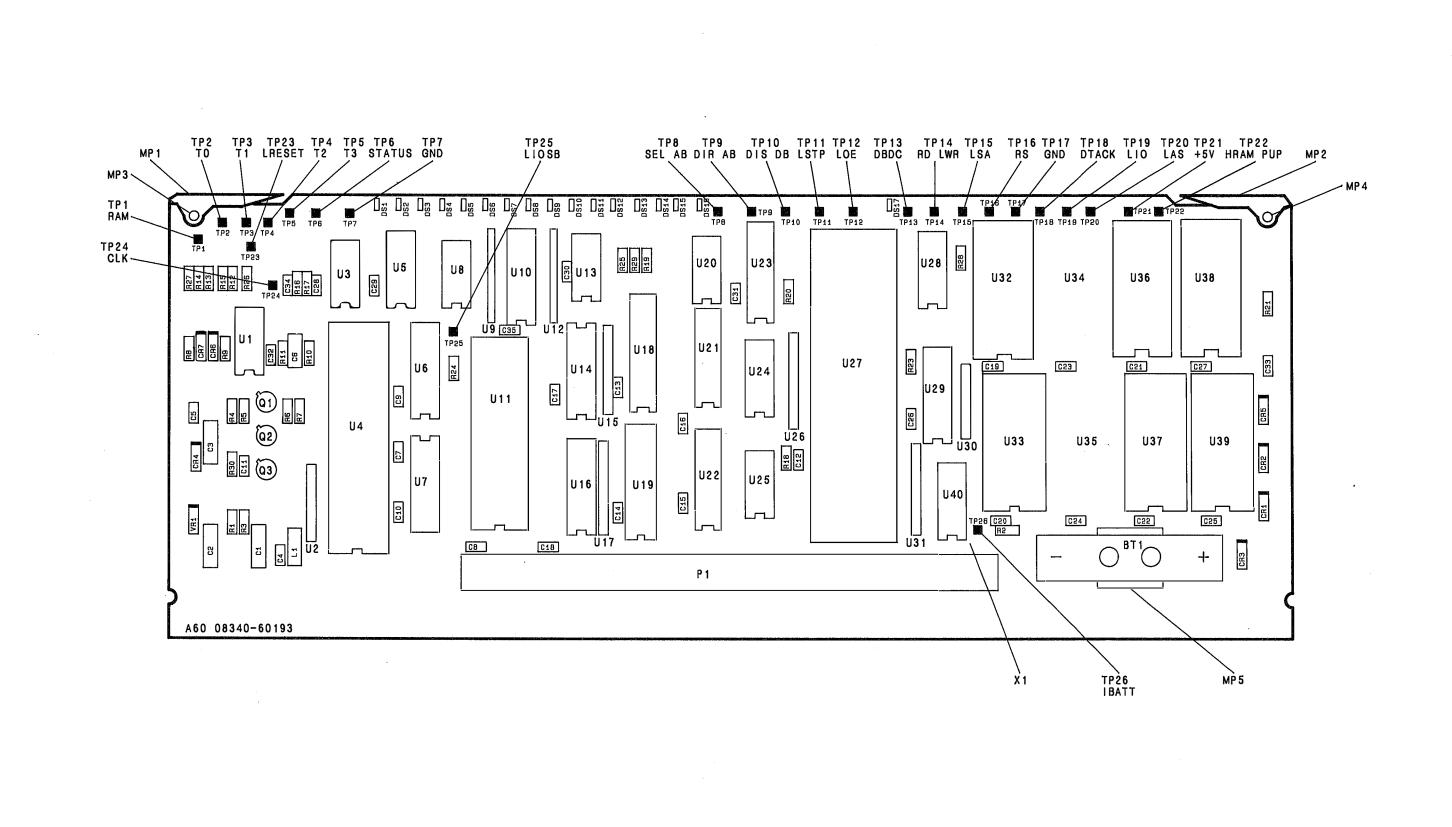

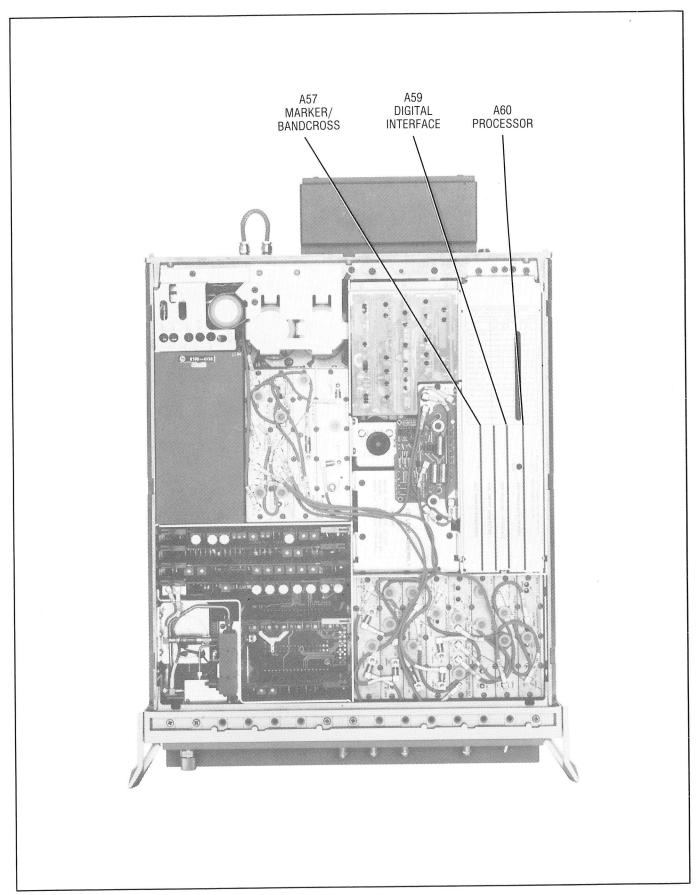

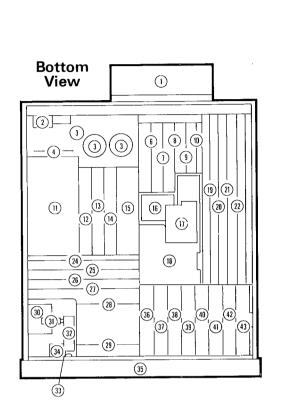

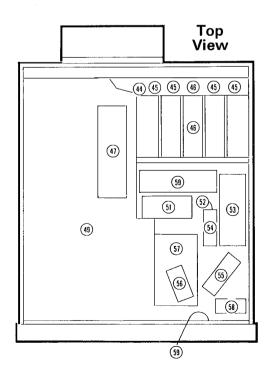

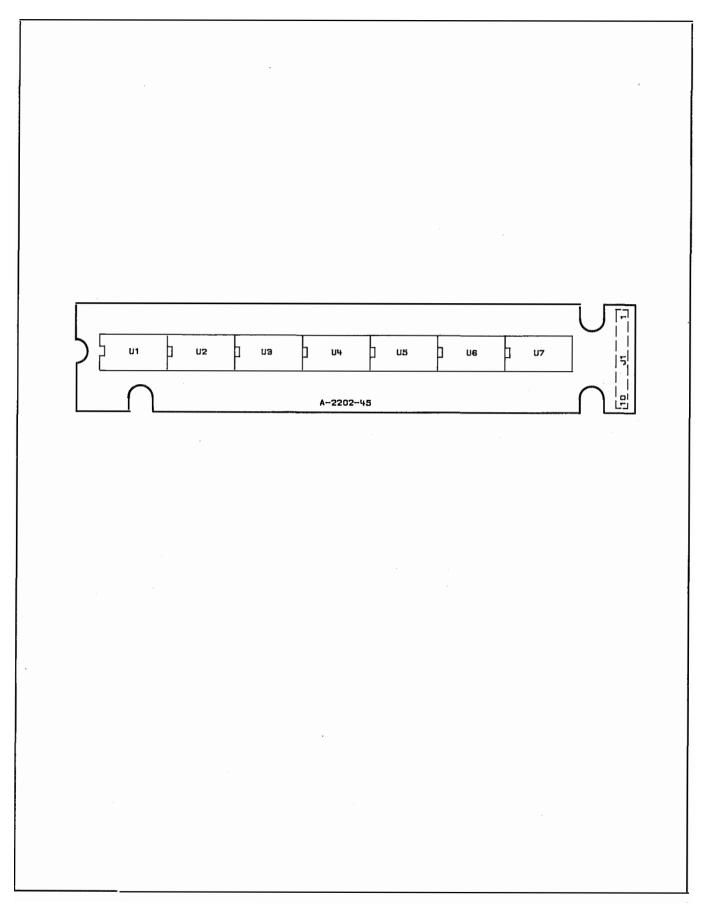

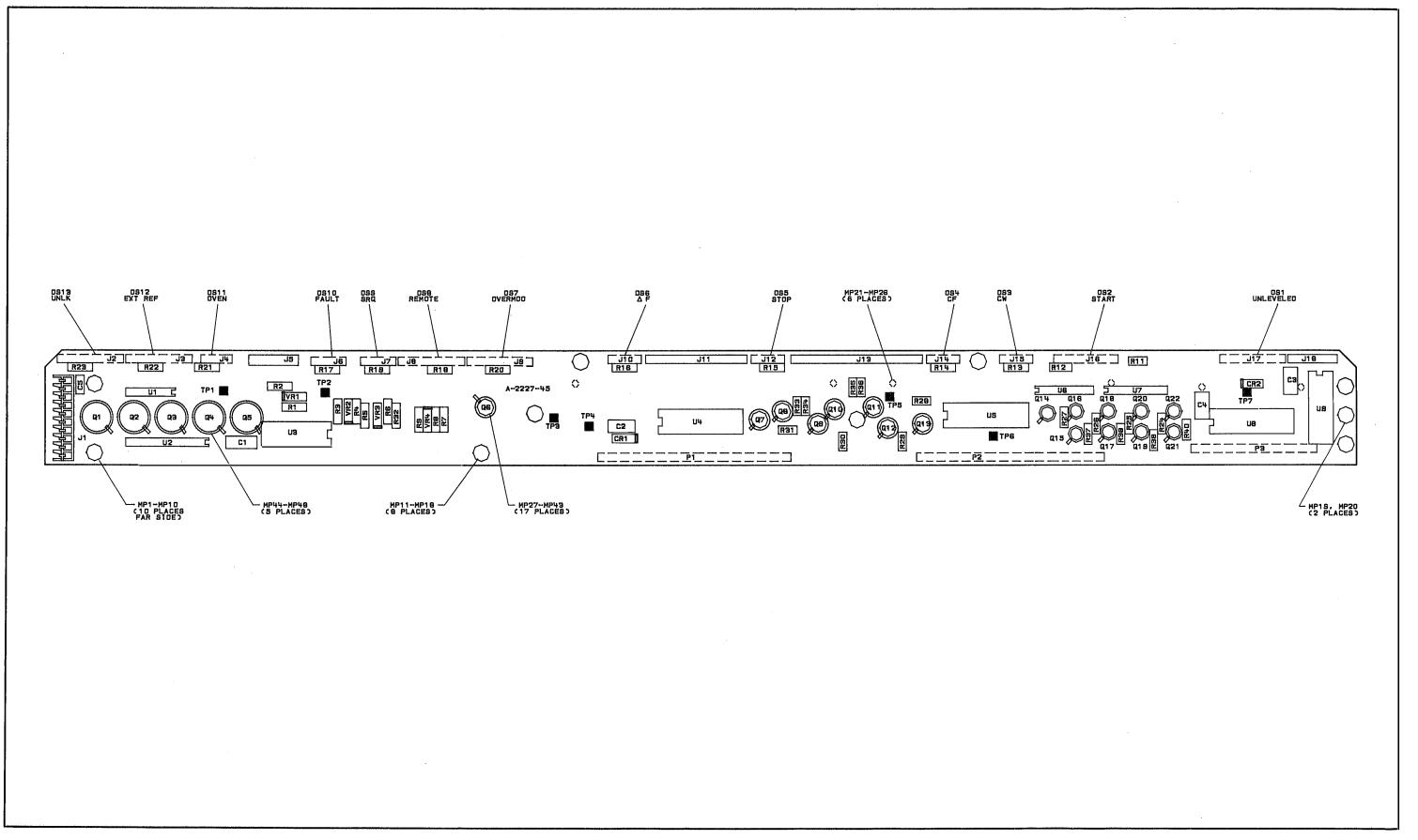

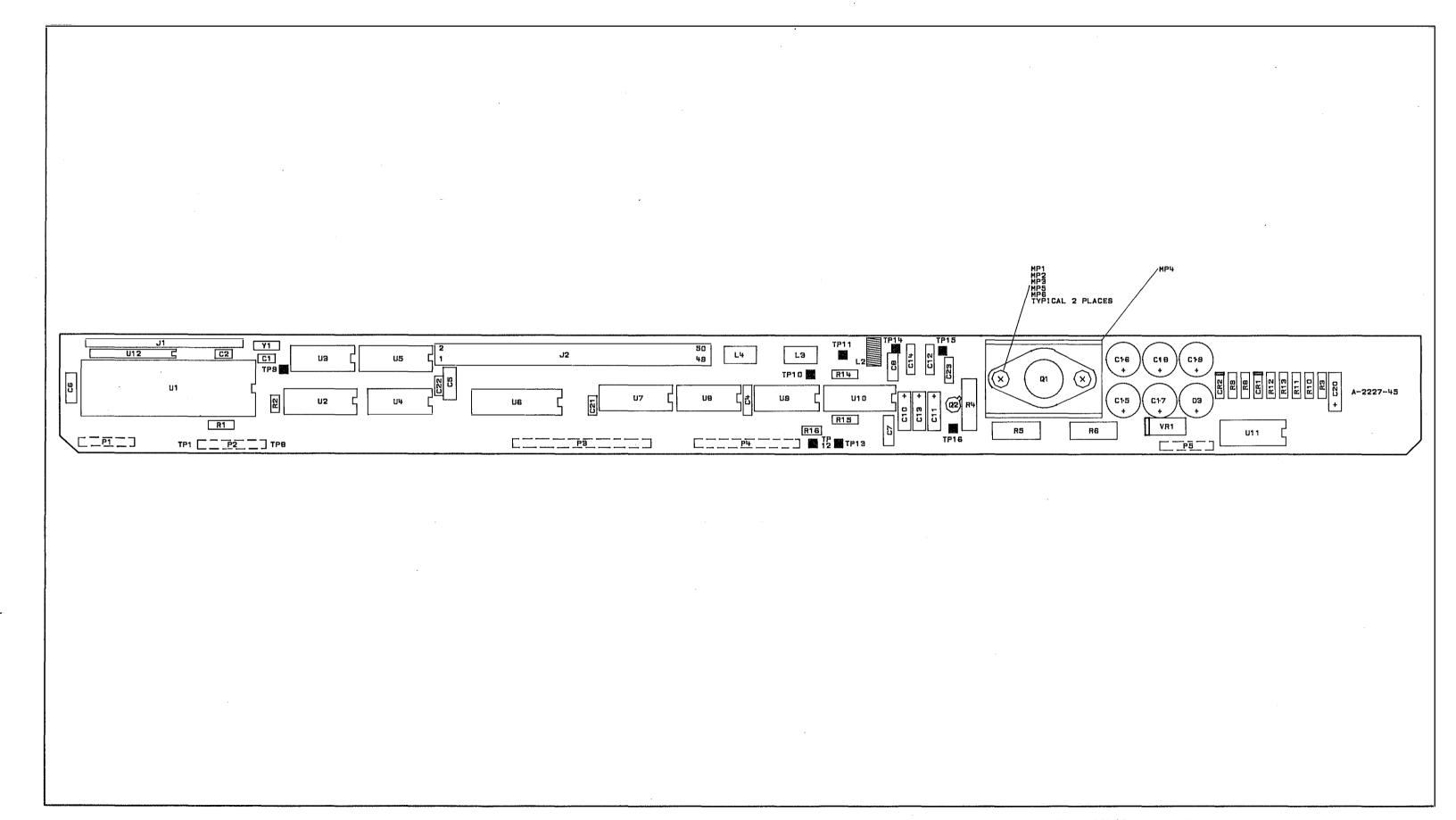

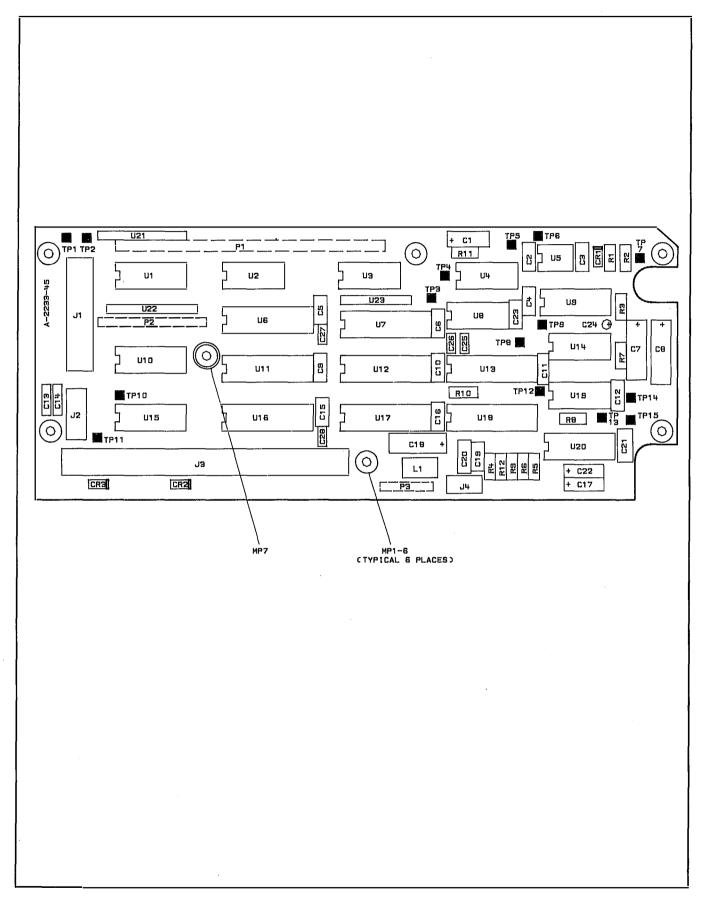

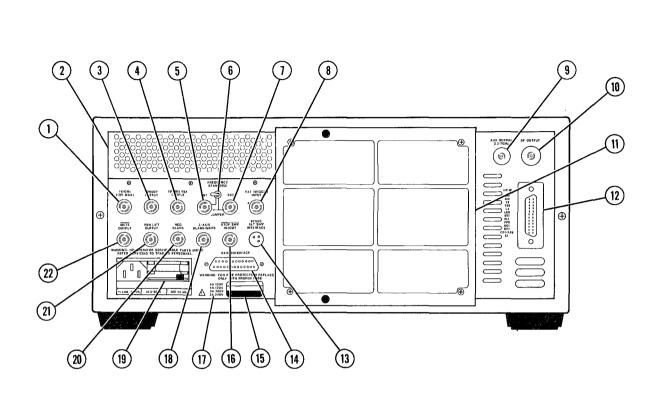

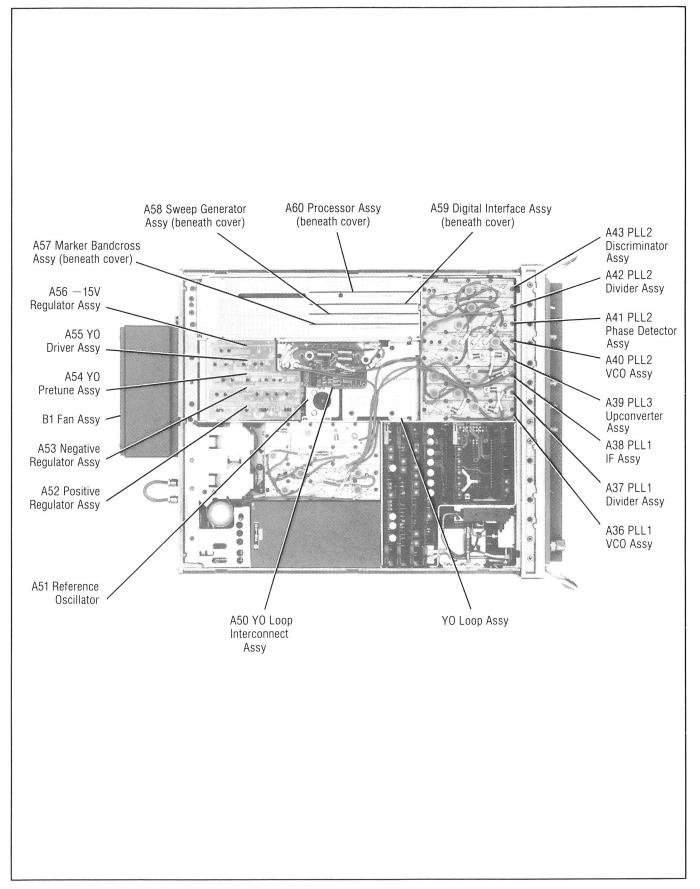

CONTROLLER SECTION MAJOR ASSEMBLIES LOCATION DIAGRAM

## CONTROLLER INTRODUCTION

The controller functional group consists of three assemblies:

A57 Marker/Bandcross board A59 Digital Interface board A60 Processor board

The following service information contains the theory of operation, schematic diagrams, component location diagrams, and troubleshooting information for all of these boards. A table of contents on the binder tab that precedes this section shows the organization of this information.

Several troubleshooting approaches are documented in this section, including:

Self Test

Direct addressing of I/O devices

by front panel key entries. (Direct I/O Addressing)

Checks of individual circuitry

The troubleshooting information in the A60 Processor board service section describes all of these procedures as they apply to the entire functional group, and this is where you should begin. The troubleshooting information in the service section of the other boards applies only to the individual boards.

The first troubleshooting test should always be the 8340A's self test that is run automatically either at power-on, or following an instrument preset.

The second troubleshooting step is to observe the 16 LEDs on the A60 Processor board. A fault diagnostic table that interprets these LEDs is contained in the A60 Processor board troubleshooting section.

The direct I/O method of troubleshooting is useful when other, non-controller group boards are contributing to the service problem; direct I/O methods can check boards throughout the instrument. These methods are described in the general troubleshooting information found at the beginning of Section VIII in the Service Introduction. The A60 Processor troubleshooting section, as mentioned above, has a truncated version of this same information.

#### THEORY OF OPERATION

#### CONTROLLER SECTION - OVERALL DESCRIPTION

The controller group contains 3 PC boards:

A57 Marker/Bandcross board A59 Digital Interface board A60 Processor board

The A60 Processor will still operate if the A57 and A59 boards have been removed from the instrument.

The HP 8340A has a 16-bit I/O data bus (DB 0-15) and a 5-bit I/O address bus (ADR 0-4) which runs throughout the instrument. The I/O data bus is bidirectional, it sends and receives data from the instrument's various digital circuits.

The [INSTR PRESET] key on the front panel activates the Low-Instrument-PreSet signal (LIPS). The LIPS signal is also generated when the instrument is turned on. LIPS initiates several events in the controller, these are:

Override the A59 board's ability to shut down the processor.

Disable access to RAM.

Reset both the instrument and display processors.

Activates all front panel LEDs as well as the 16 self-test LEDs.

The self test LEDs are located on the A60 Processor board.

When LIPS is released the controller performs a self test containing the following steps:

Instrument processor internal registers are checked.

RAM is partially checked.

ROM is checked.

I/O address bus (ADR 1-5) is checked.

1/O data bus (DB 0-15) is checked.

The checksum of the calibration data is verified.

Refer to the Calibration Constants description in the Service Introduction.

The Analog-to-Digital Converter (ADC) is checked.

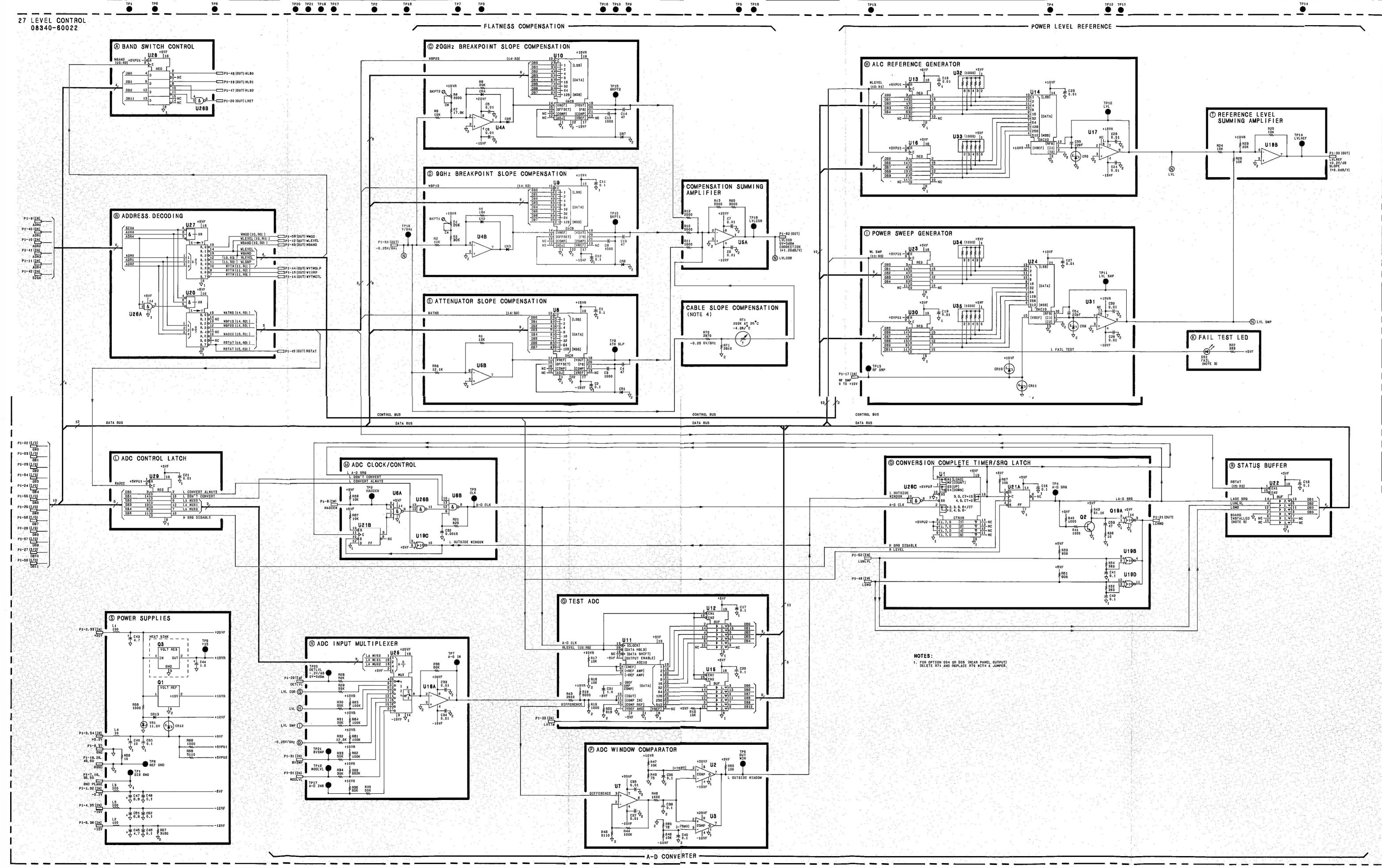

This circuit is located on the A27 Level Control board. The ADC is essentially an internal voltmeter which allows the instrument processor to monitor several de levels in the instrument. Examples of these are; Modulation level, sweep voltage, and ALC level.

If the self test was initiated by an [INSTR PRESET], the instrument sets all front panel functions to a preset condition and begins operation.

If the power switch was just turned on, a signal called "Hi Power UP" (HPUP) goes low. This signal tells the processor that, after self test is completed, it should restore previous instrument settings. The current instrument state, as well as all SAVE/RECALL registers, are stored in battery powered RAM for this purpose.

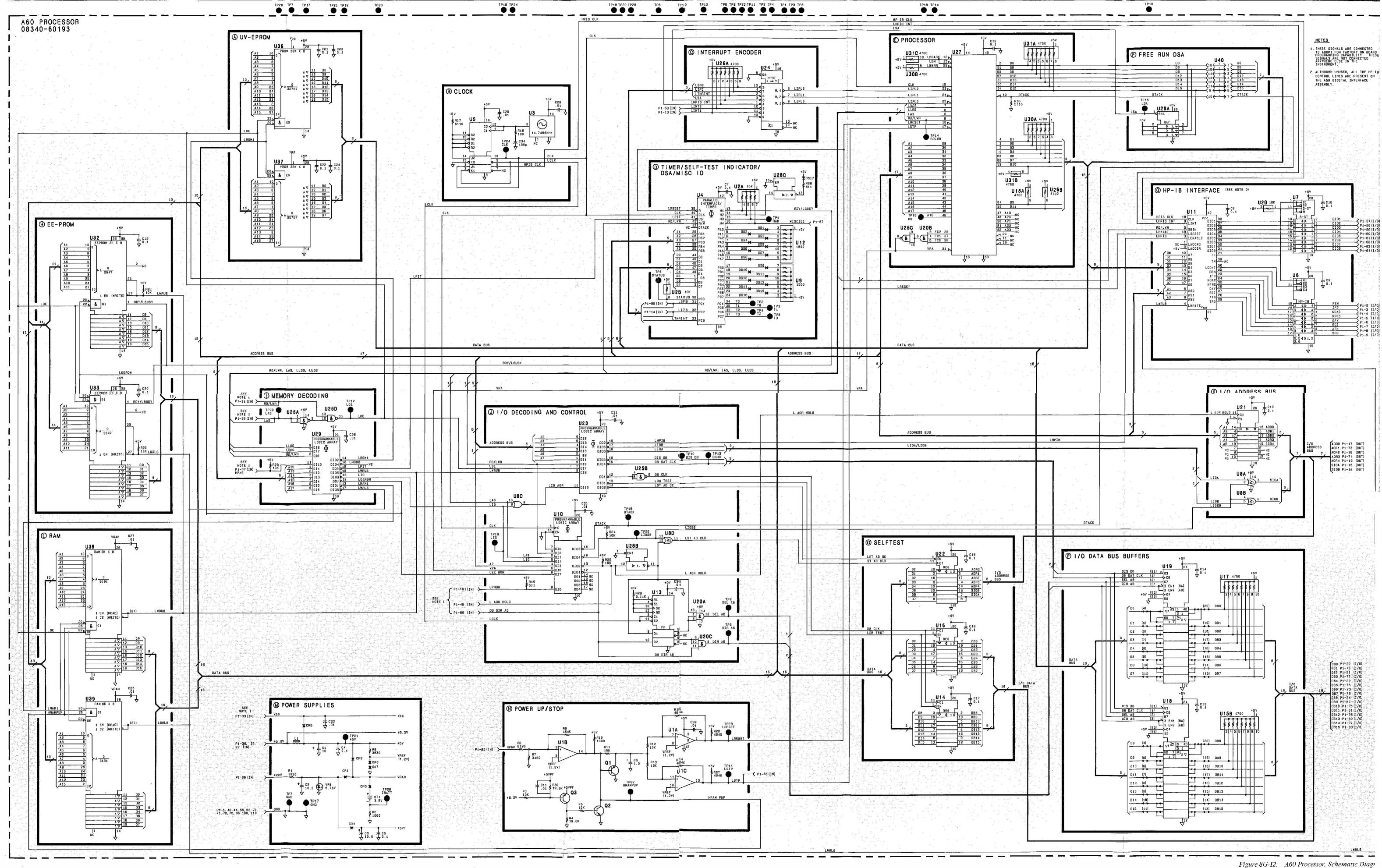

#### Processor and Memory Description

The heart of the controller is a 16 bit microprocessor. This processor directly interfaces with RAM and ROM.

Memory consists of the following:

#### UV ERASABLE PROGRAMMABLE ROM - 32k x 16.

The instruments firmware is stored in this memory as well as default calibration data.

#### ELECTRICALLY ERASABLE PROGRAMMABLE ROM - 2k x 16.

Protected calibration data is stored here.

#### RAM - 8k x 16.

Working calibration data and SAVE/RECALL register values are stored in RAM. A backup battery provides power to the RAM for at least one year when the instrument is disconnected from ac mains (or if the processor board has been removed from the instrument).

If the backup power to the ram should fail, working calibration data and SAVE/RECALL register information will be lost. When the instrument is turned on, protected calibration data will be placed in RAM and "CALIBRATION RESTORED" will be displayed in the front panel ENTRY display.

#### A59 Digital Interface Assembly Description

The digital interface links the processor to the sweep generator, M/N oscillator, and the 20-30 synthesizer. The microprocessor read/write strobes are used to enable either buffers that send data to the processor, or clock registers that store data sent from the processor. Several of these strobes operate registers located on other assemblies. For example, the phase-lock indicators allow the controller to determine which of the instrument's phase-lock loops are unlocked, while the M/N controls are registers that operate the M/N oscillator.

The digital interface connects to the 16-bit data bus (DB 0-15). By use of the LSTP (Low SToP) signal, this assembly has the ability to stop all processor operations. When the processor stops, the green "RUN" LED on the processor board is turned off. LSTP stops the processor when it is not needed, or when it is necessary to eliminate all potential sources of digital noise (e.g. during forward sweeps). When the LSTP signal releases the processor to perform a task, the processor defers processing until it determines that the LSRQ (Low Service ReQuest) signal is low. LSRQ can be sent low by the digital interface or by the front panel processor. Once LSRQ is sensed low it can go high again and the processor will still finish all pending tasks before checking this signal again.

By use of the change detectors and the processor SRQ blocks, the controller responds to the following:

Changes in the UNLOCK or OVEN indicators Changes in OVERMOD or UNLEVELED conditions Changes in the "EXTERNAL REFERENCE" switch position. Any keystroke or RPG activity.

The processor also distinguishes between Power On and Instrument Preset, and responds to sweep events as indicated by the marker bandeross assembly.

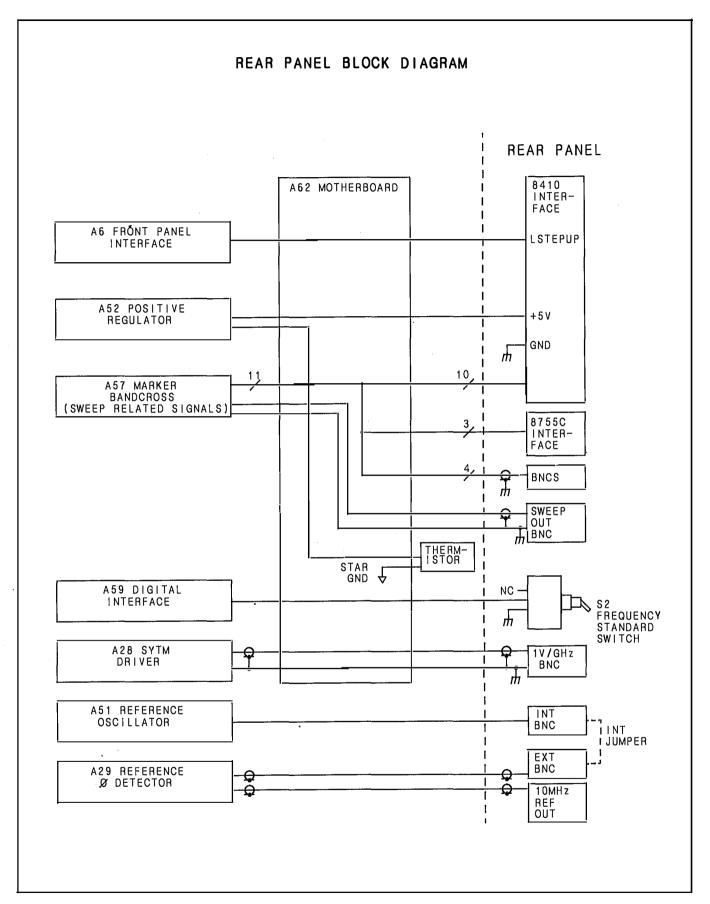

#### A57 Marker/Bandcross Assembly Description

The marker bandcross assembly generates markers, controls the start and stop sweep points, and determines bandcrossing points. The marker/bandcross board also provides the front and rear panel sweep signal as well as several other rear panel interface signals. The sweep-event memory stores numbers that correspond to voltages on the 0-10 volt sweep signal. Each number stored in the memory represents a single sweep event. Sweep events are detected by the sweep comparator, which compares them against the 0-10 volt sweep ramp. Sweep events include:

Turning markers on and off.

Stopping the sweep for a bandcrossing.

Stopping the sweep for the end of sweep and retrace.

The manual sweep DAC is used to offset the sweep-out signal when the instrument is in CW or Manual mode. This DAC is also used as part of an algorithm to find the current sweep position when changes are made in frequency parameters during an analog sweep longer than 300 ms.

The sweep control block provides the capability of starting and stopping the sweep either from the rear panel or by the sweep comparator. CRT Z-axis control circuits provide the capability of blanking the sweep on a display for bandcrossings or retrace. Z-axis control is also used to intensify the display for markers.

The marker/bandeross board uses the LBX (Low Bandeross) signal to stop the analog sweep at positions previously loaded in the sweep event memory by the processor. When LBX is low, the A59 Digital Interface causes the processor to run, allowing the processor to perform the tasks necessary for the sweep to proceed. This will be either at a banderossing, or at a retrace at the end of a sweep.

#### **CONTROLLER SECTION**

#### TROUBLESHOOTING TO ASSEMBLY LEVEL

The controller functional group consists of the A57, A59, and A60 assemblies. Troubleshooting this section should begin by going to the Overall Instrument Troubleshooting guide in the Service Introduction. There are generally three levels of troubleshooting for these boards.

#### Self Test

The self test is run on Power-On after pressing [INSTR PRESET]. Two front panel LED's, CHECK I and II, give a visual indication of the self test results. These indicators, and their meaning, are explained in in the above mentioned portion of the Service Introduction.

#### Front Panel Initiated Direct I/O Addressing tests

The front panel can be used to write to or read from any I/O device.

#### Component Level Troubleshooting

Schematic diagrams, circuit theory, and troubleshooting information are provided.

The component level troubleshooting section associated with the A60 Processor board has the majority of the Controller functional group assembly level troubleshooting. Therefore, some diagnostics for A57 and A59 are also included in this section.

Problems in either the A57 Marker/Bandeross or A59 Digital Interface assemblies show up indirectly in other areas of the instrument's operation. Therefore, most troubleshooting for A57 and A59 should be done first through the overall instrument troubleshooting guide (located in the Service Introduction).

#### REPAIR PROCEDURES

#### BATTERY A60B1 REPLACEMENT

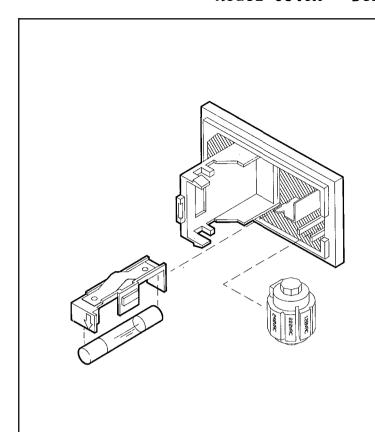

A60BI (HP Part Number 1420-033I) provides backup power to the instrument's RAM IC's. This RAM holds working calibration data and the SAVE/RECALL register values. When the battery is defective or replaced, the above information will be lost. However, as soon as the instrument is reassembled and turned on, the protected calibration data stored in EEROM will be retrieved and placed in RAM. "CALIBRATION RESTORED" will be displayed in the instrument's ENTRY display

This battery will provide backup power for at least two years, and has a shelf life exceeding 10 years. It is not rechargeable.

#### NOTICE

A60BT1 has a strong outer case. The case has been shown to remain intact even when the battery is shorted or forcibly charged at a rate not exceeding 50 ma. However, if the battery is abused mechanically, electrically, or thermally, the following warning should be taken into account.

#### WARNING

This battery contains Lithium and Thionyl Chloride (SOCL<sub>2</sub>), the latter in liquid form. If abused, this battery represents a fire, explosion, and severe burn hazard.

Lithium can burn or explode on contact with moisture in the air or water.

Thionyl Cloride is highly toxic, and on contact with air will partially break down into Hydrochloric acid and Sulfur Dioxide fumes which are also toxic and are extremely repulsive, strongly irritating, and are corrosive to the eyes, skin, lungs, and mucous membranes. CONTACT A POISON CONTROL CENTER OR DOCTOR IMMEDIATELY if a person comes in contact with or breathes this material.

Do not attempt to charge this battery, as this may cause it to rupture.

Do not damage or attempt to open the battery.

Do not heat above 212 degrees Fahrenheit (100 degrees Celsius), expose contents to water, or incinerate. Determine if state and local laws require disposal of Thionyl Chloride or Lithium in a chemical waste disposal site, or return the battery to the Hewlett-Packard Company, 1412 Fountaingrove Parkway, Santa Rosa, Ca. 95401, Attention: Environmental Engineering Department.

Batteries that are dead have converted most of the Lithium and Thionyl Chloride into non-toxic chemicals.

#### Replacement Procedure

#### CAUTION

The assembly mentioned below contains static sensitive components. Any work performed on instrument PC board assemblies should be done at a work station equipped with an anti-static surface. Any persons working on this instrument should wear a grounding strap that provides a path to earth ground of no less than 1 Megohm and no more than 2.5 Megohms. All anti-static safeguards must conform to state and federal safety standards and statutes. When handling a PC board always hold it by the edges. Never touch the finger contacts.

- 1. Disconnect ac mains from the instrument. Wait three minutes before proceeding to step 2.

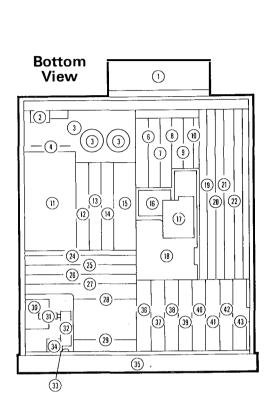

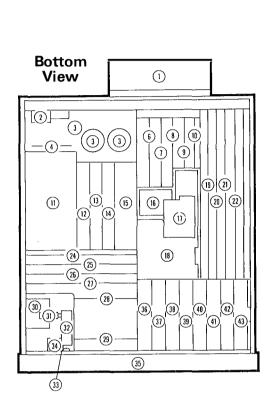

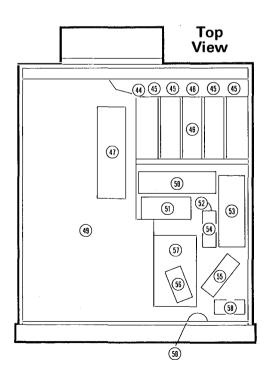

- 2. Remove the instrument's top cover and remove the A60 Processor board. Refer to the front of any Service Section tab for an assembly location guide, if necessary, to locate this assembly.

- 3. Remove the battery and dispose of it in a safe manner, i.e. do not damage or incinerate it. This battery is not rechargeable. Do not attempt to charge it or internal pressure may cause it to rupture. Measure the voltage of the new battery before installing it. The voltage should be about 3.6 Vdc. Test the battery by placing a 10K Ohm resistor across it and measuring the voltage output. The voltage should not drop to less than 3.4 Vdc. If the battery is within voltage tolerance, install it. Do not set the A60 Processor on bare metal as this may short out the new battery, possibly damaging it

- 4. Reinstall the A60 Processor board. Replace the top cover and turn the power switch ON. "CALIBRATION RESTORED" will be displayed in the front panel ENTRY display.

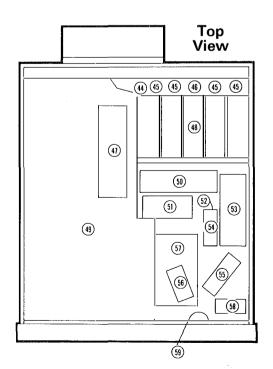

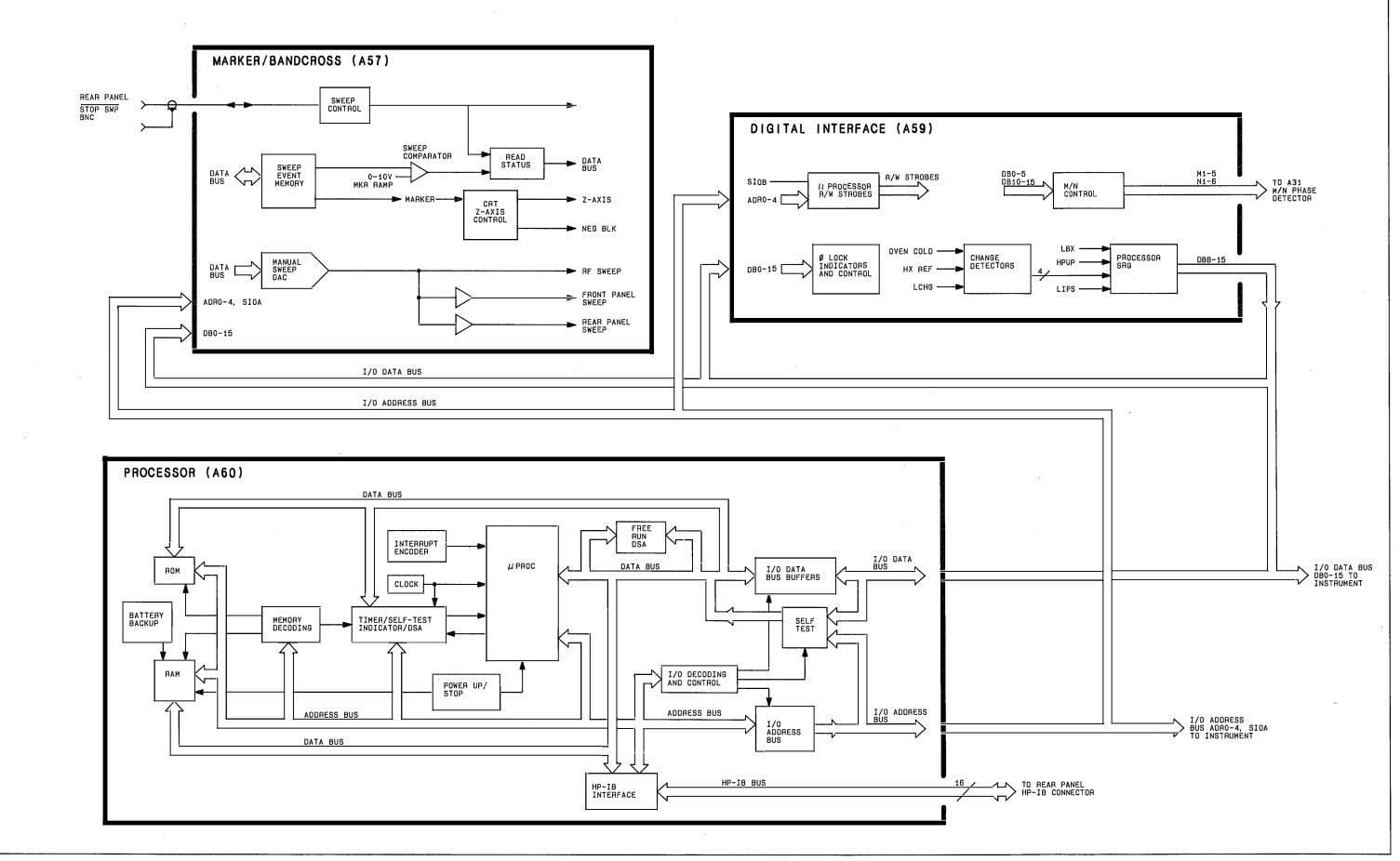

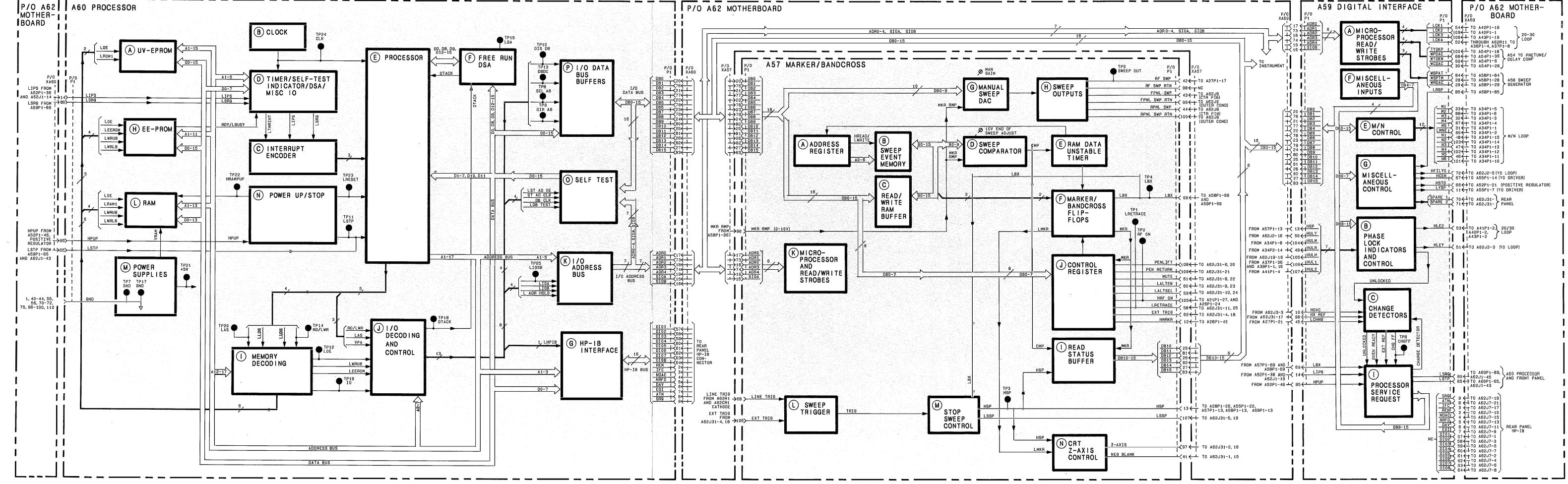

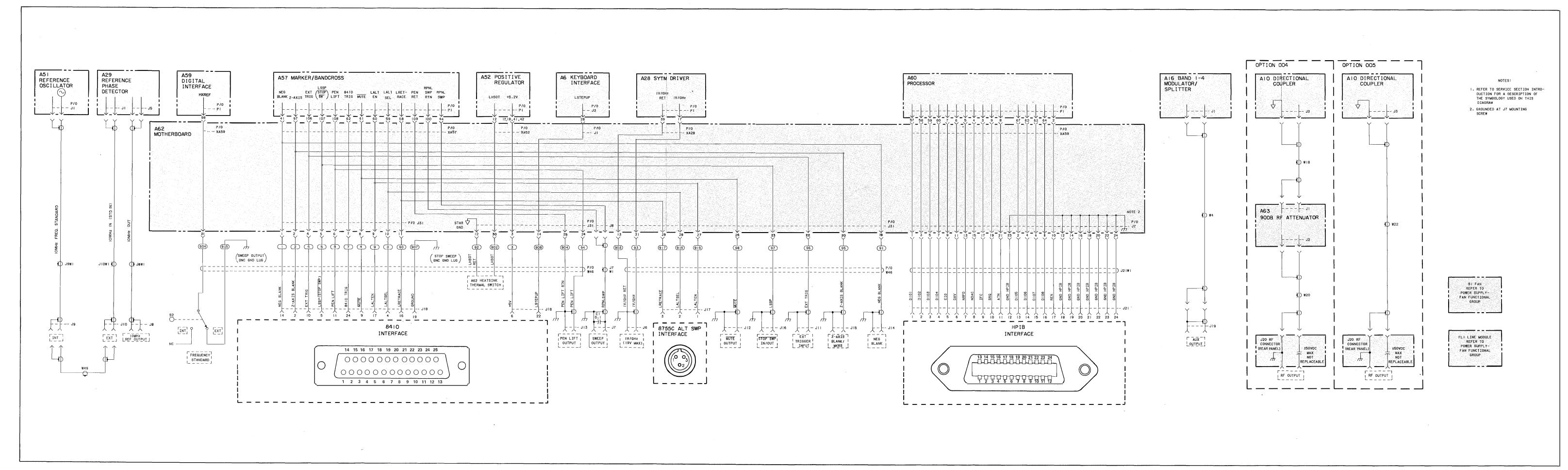

Figure 8G-1. Controller Section Simplified Block Diagram 8-435/8-436

Figure 8G-2. Controller Section Block Diagram

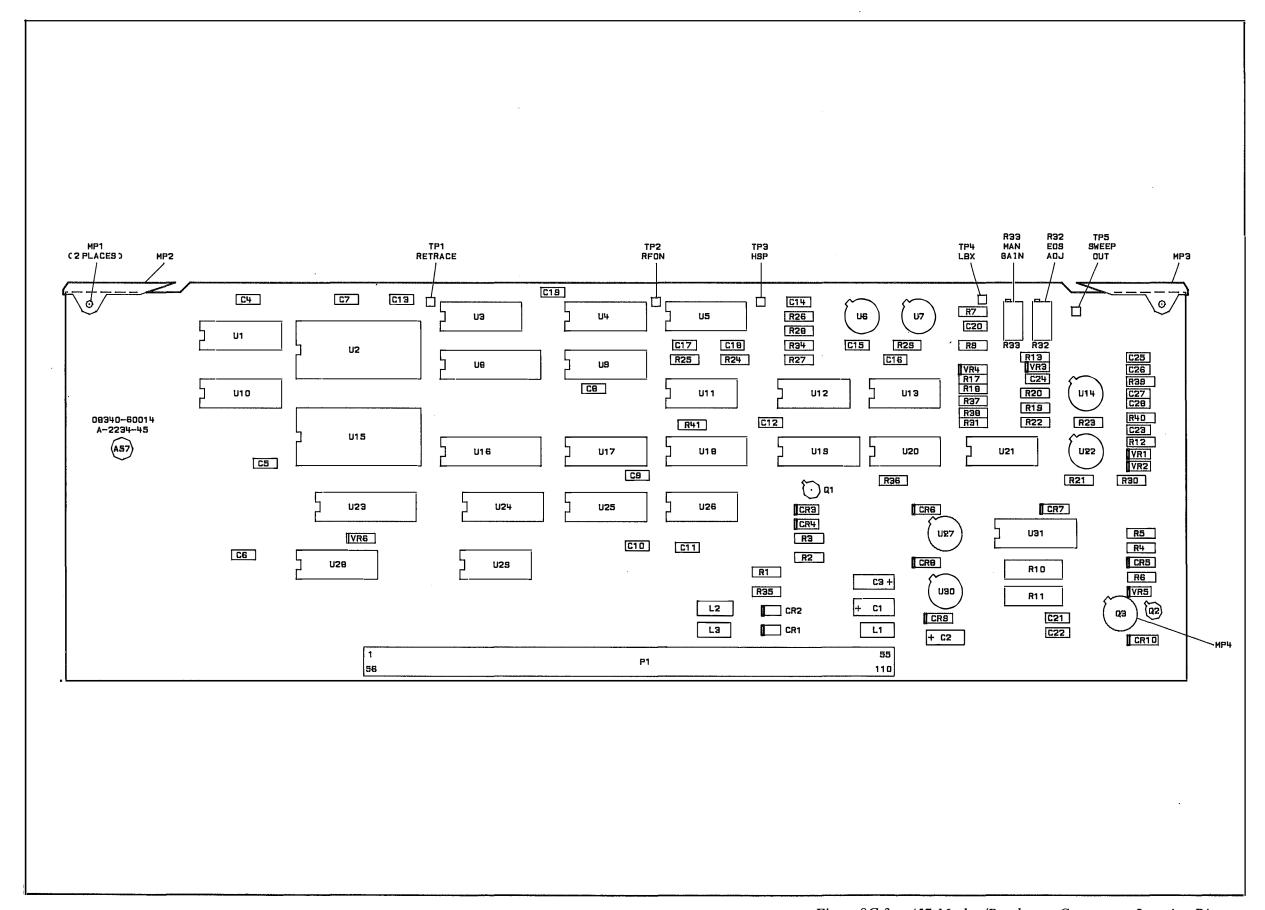

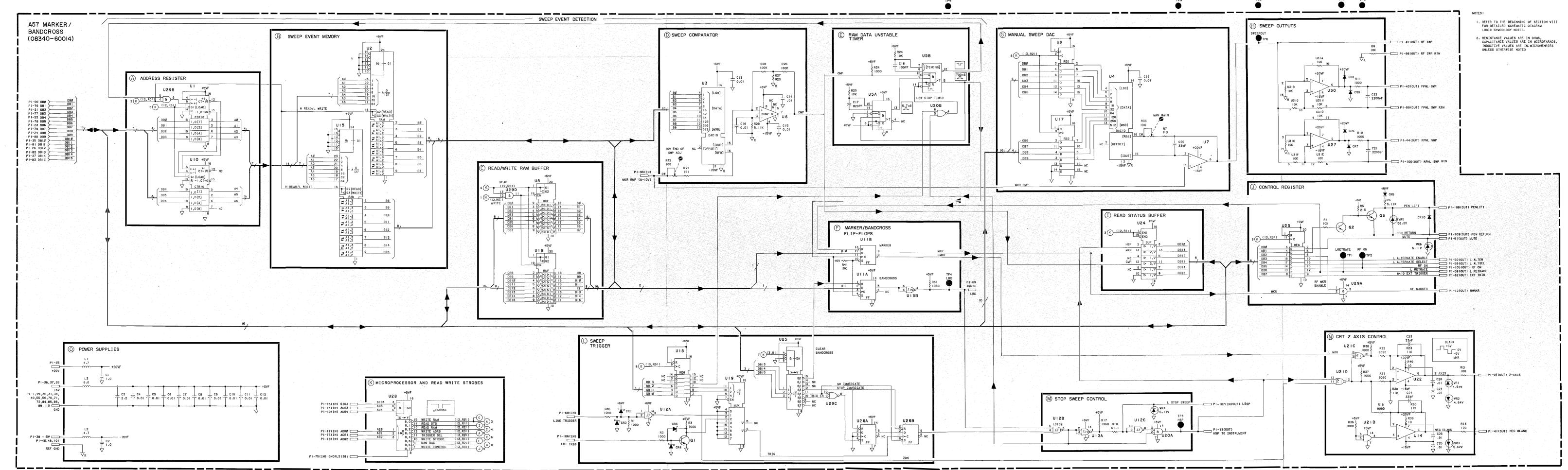

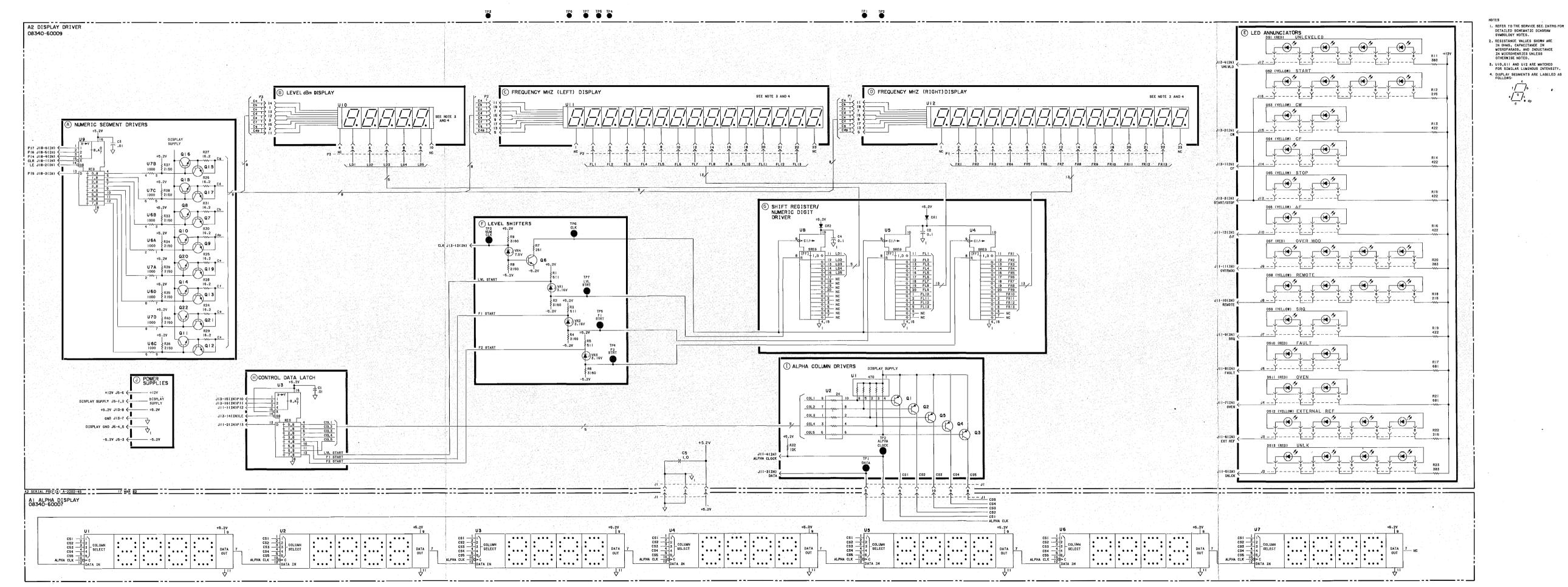

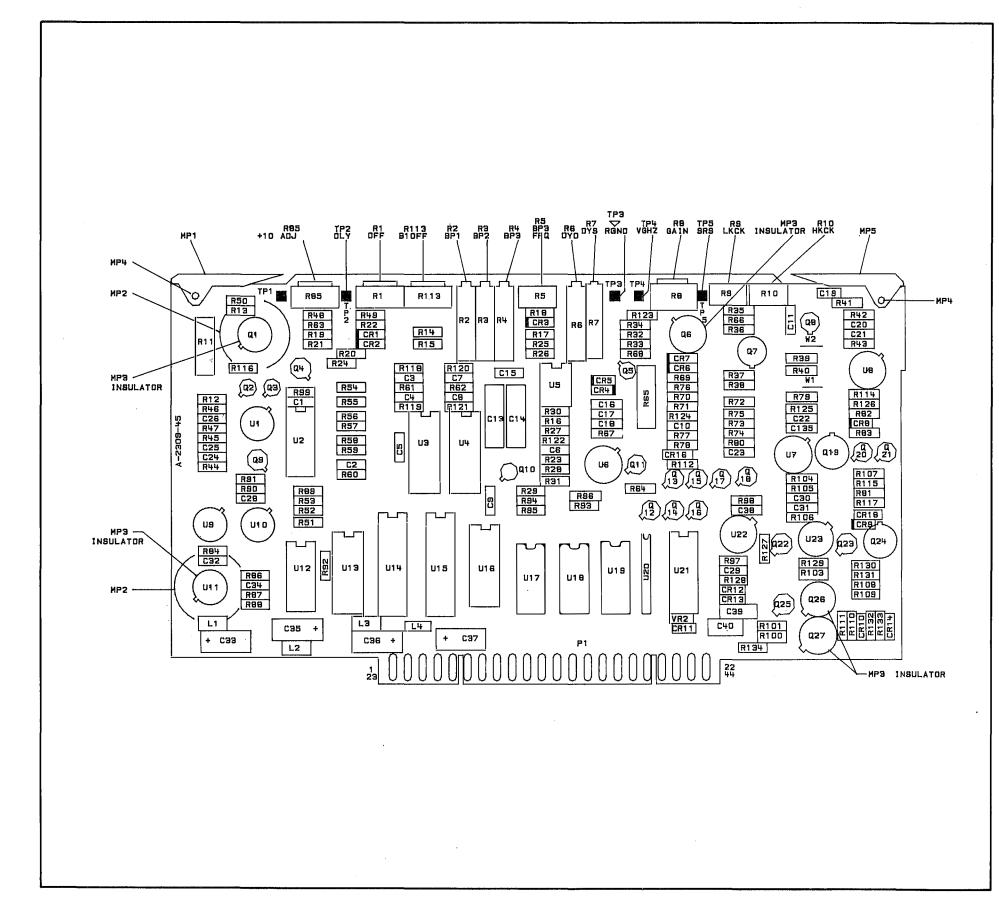

## A57 MARKER BANDCROSS ASSEMBLY, CIRCUIT DESCRIPTION

#### INTRODUCTION

The A57 Marker Bandcross board generates the Z-axis signal required to place intensity markers on a CRT. If enabled by the front panel, amplitude markers will be generated by sending a marker signal to the leveling circuits. The same circuits that detect markers are used to detect band crossings or the end of sweep. These circuits will cause the sweep to be stopped and the microprocessor to be activated. Other circuits interface with rear panel interface connections. Hardware on this board is used during self test to verify the operation of the 16-bit microprocessor data bus.

#### SWEEP EVENT DETECTION (BLOCKS A, B, C, D, E, AND F)

A sweep event is a Marker, a Band Crossing or the End of Sweep. Prior to the beginning of a sweep, the microprocessor will store in the Sweep Event Memory (Block B) a series of numbers which correspond to all the sweep events that are to take place during a sweep. These numbers are loaded in the following manner:

- 1. The processor sets the Address Register (Block A) to 0 (i.e., sets DB0-6 to zero then outputs address 12,R3:)

- 2. The processor writes into the Sweep Event Memory (Block B) a series of numbers corresponding to the sweep events. The Address Register (Block A) is automatically incremented after each write to memory (address 12,R0: to Ul pin 5).

- 3. The processor sets the Address Register (Block A) back to 0.

Before a sweep begins, the processor determines how many sweep events there will be in the sweep. For example, for a sweep containing one bandcrossing and a marker, there would be four sweep events: two for the marker, one for the bandcrossing, and one for the end of sweep. The processor then computes at what point in the sweep each event occurs and converts this information to a number from 0-999 which corresponds to the 0-10V sweep. This series of numbers is written into the Sweep Event Memory (Block B) via data lines B0-B9. When the Address Register (Block A) is set to location 0, the first number stored in the memory appears at the input of the Sweep Comparator DAC U3 (Block D). The DAC converts this number to a voltage between 0-10V. This voltage is not available at the output of U3 but is compared internally to the MKR RMP (marker ramp) 0-to-10V signal. When the MKR RMP rises to a voltage equal to the value at which the DAC is set, the output of U3 (pin 15) will fire comparator U6, and the

first sweep event occurs. This causes the Marker and the Bandcross flip flops (Block F) to be clocked. The data stored in the flip flops and taken from data bits 10 and 11 of the RAM (Block B, U15) determines what kind of sweep event will occur. A marker is created by two sweep events. The first event turns the marker on; the second turns the marker off. Markers are 1/1000 of the display width. When a user attempts to change one of the frequency parameters in the middle of a slow sweep (300 ms or longer), the Sweep Event Detection circuitry (combination of Blocks A through F) determines the position of the sweep, allowing the instrument to phase-lock to a frequency appropriate to the current sweep position. For faster sweep times, the instrument will wait until the beginning of the next sweep to make frequency changes.

#### ADDRESS REGISTER A

Ul and UlO comprise a 6 bit counter register. The counter is preset when the microprocessor writes to I/O address 12,R3: via Ul pin 11. The Address Register can be counted or incremented two ways: first by the microprocessor writing to I/O address 12,R0:, and secondly when timer U5B (Block E) fires. The signal from U5B indicates that a sweep event has occured and that the Sweep Event Detection circuitry (Blocks A through F) should get ready for the next sweep event. The outputs of the Address Register (AO through A6) are used to address the Sweep Event Memory (Block B).

#### SWEEP EVENT MEMORY B

U2 and U15 are RAMs each containing 128 8 bit bytes. They are combined to provide 128 16 bit words of memory. Sweep events are stored into the RAM when the microprocessor does a write to I/O address 12,R0:. U8 and U16 (Block C) are buffers through which the microprocessor reads or writes RAM data. The RAM is addressed by the Address Register (Block A). In normal operation of the instrument, only about 15 of the 128 words of RAM are used. Each location used corresponds to a single sweep event that is to occur during the sweep. The RAM has stored in it, the position along the sweep where each event is to occur, as well as informaton indicating what kind of sweep event each one is.

#### READ/WRITE RAM BUFFER C

U8 and U16 make a 16 bit bidirectional buffer which connects the microprocessor with the Sweep Event Memory (Block B). When the microprocessor sends I/O Address 12,R0:, the buffer transfers data from the instrument data bus (DBO thru DB15) to BO thru B15. When the microprocessor sends I/O Address 12,R2: data is transfered the opposite direction (i.e., from the Sweep Event Memory to the microprocessor).

#### SWEEP COMPARATOR D

U3 is a 10 bit DAC which compares the 0-to-10V MKR RMP (marker ramp) to the binary number placed at its input by the Sweep Event Memory (Block B). The MKR RMP (0-10V) is connected to the V-Feedback input of U3 (pin 16). At the beginning of a sweep, the output of the DAC will be below 0 volts. When the voltage applied by the MKR RMP (0-10V) is equal to the corresponding digital number at the DAC's input, the output will go above 0 volts. Comparator U6 is set to trip when the output of the DAC rises above 0 volts. For example if a Sweep Event is to occur at mid-sweep, the following conditions would exist: the DAC would have the number 500 decimal or 111110100 binary placed at its digital input. Before the Marker Ramp gets to 5 volts, which represents the exact middle of the sweep, the DAC output would be below 0 volts and Comparator U6 output (pin 7) would be LOW. As the MKR RMP approaches 5 volts, the output of the DAC would approach 0 volts. When this occurs, the comparator will fire, causing its output to go HIGH. When the comparator fires, R28, R26 and R27 cause a 2 mV offset to be made to the positive input of the comparator (pin 2). This ensures that the comparator that just fired will not change states due to noise on the MKR RMP. R32 (10V END OF SWP ADJ.) is adjusted to make the end of sweep voltage equal 10.000 V.

#### RAM DATA UNSTABLE TIMER E

This circuit debounces the output of the Sweep Comparator (Block D) and causes the Address Register (Block A) to be incremented after each sweep event has been detected. U5B is triggered by the comparator firing and outputs a 700 ns pulse. The pulse sets timer U5A and also clocks the Marker/Bandcross Flip-Flops (Block F). Timer U5A resets after 5.7 us and is used to keep Timer U5B from being fired again until the circuits in Blocks A, B, C, and D have had time to settle following a sweep event. U20B controls the reset input of Timer U5B. The inputs of U20B are used to disable the timer. pin 5 of U20B is connected to U12B pin 6 (Block M) and is HIGH when the sweep is stopped. This keeps the timer from firing after the sweep has been stopped. pin 6 of U20B is controlled by the microprocessor through register U18 (Block L). This is set HIGH to disable the timer when the instrument does its self-test.

#### MARKER/BANDCROSS FLIP-FLOPS F

UllB and UllA are used to store B10 and B11 from the Sweep Event Memory (Block B). These two signals indicate what kind of sweep event is to take place. Bit 10 is connected to UllB pin 12 and sets the state of the MKR control line connected to its output

(pin 9). When a Bandcrossing occurs the sweep will be stopped so that the microprocessor can initiate phase-lock for that bandcrossing. This is done by the LBX signal. When a Marker occurs, the sweep is not stopped and the marker is generated as the sweep progresses.

#### MANUAL SWEEP DAC G

The manual sweep DAC U4 is used only in MANUAL SWEEP mode. A binary number between 0-1000 is written to the DAC. The digital input of the DAC is connected to registers U9 and U17. The microprocessor is connected to U9 and U17 via the I/O Data Bus. Data is clocked into these registers by strobe 13,R2: (Block K). In MANUAL SWEEP mode the MKR RAMP should always be at 0 volts. The U4 DAC converts its digital input to a voltage (0 to -10 V) at its output, U4 pin 15. The Op Amp, U7, will invert this signal to provide the 0 to +10V SWEEP OUT at TP5 (Block  $\mathbf{H}$ ).

The SWEEP OUT of Block G (U7 pin 6) is the result of either the manual sweep DAC, U4, when MANUAL SWEEP mode is selected, or the MKR RAMP when MANUAL SWEEP is not selected.

When the instrument is not in MANUAL SWEEP mode the input of the DAC is set to 0 by the microprocessor and the MKR RAMP is simply buffered by Op Amp U7.

The MAN GAIN (manual gain) adjustment, R33, is adjusted to obtain 10.000V at the sweep output when in MANUAL SWEEP and the manual frequency is set to the maximum possible value for a given sweep. For example: Set R33 to obtain 10.000V at TP4 when MANUAL SWEEP is on and the rotary knob is turned clockwise until the manual frequency is equal to the STOP frequency.

#### SWEEP OUTPUTS H

The SWEEP OUT is buffered by U30 and U27 which are connected to the front and rear panel Sweep Output connectors. Floating grounds are needed to eliminate ground loops which would cause 60Hz signals to appear on the sweep outputs. The front and rear panel sweep output connectors are floating. Any low frequency noise found on the floating front or rear panel sweep output connectors is connected by the RTN lines to the non inverting inputs of the buffer Op Amps. This allows the Op Amps to sense and remove this unwanted noise. C21 and C22 are provided to eliminate high frequecy noise.

#### READ STATUS BUFFER I

Buffer U24 enables the processor to monitor the state of the following signals by doing a read from I/O address 12,R1:

- 1. The Sweep Comparator (CMP) pin 12

- 2. The Marker flip flop (MKR) pin 14

- 3. The High Sweep (HSP) line, pin 2

#### CONTROL REGISTER J

Register U23 enables the processor to directly control the state of the various interface lines connected to the register. This is done when the microprocessor writes data to I/O address 13.R3:. The data is then available continuously at the output of the register.

AND gate U29A is used to control the RF Marker signal. When the RF Marker signal is HIGH, it causes the RF Power Control circuits to slightly increase the RF power. This is used as a marker. U29A pin 1 is used to turn this feature on or off.

#### MICROPROCESSOR READ AND WRITE STROBES K

The instrument processor outputs I/O address information on the I/O Address Bus (ADRO thru ADR4 plus ADR5 which becomes SIOA). U28 decodes the address and generates the appropriate strobe.

These strobes are used throughout this assembly to either clock registers causing them to store data found on the I/O data bus or to enable buffers to place data on the I/O data bus so that the Microprocessor can read it.

The outputs of U28 are LOW true pulses of about 500 ns.

#### SWEEP TRIGGER L

Multiplexer U19 selects either LINE or EXT (external) trigger when the processor outputs the appropriate bits to the instrument Data Bus (DB 10 thru DB 13), and U28 outputs address 13,R0: (Block K). The output of U18 pins 5 or 7 will select the appropriate U19 input (i.e., U18 pin 7 HIGH selects Line Trigger, U18 pin 5 HIGH selects External Trigger). U18 pin 10 is used to disable the RAM Data Unstable Timer (Block E).

The ZON (Z axis ON) line is also controlled by U18 in a similar manner. The ZON signal when HIGH will force the Z-Axis line (Block N) to be +5V. U25 is a 3 to 8 decoder which generates 500 ns pulses at its output each time the microprocessor writes to I/O address 13,Rl:. By writing appropriate numbers to this register, the following events can occur:

- Start the Sweep (U25 pin 11)

- Stop the Sweep (U25 pin 12)

- ☑ Trigger Enable (U25 pin 10)

- $\boxtimes$  Clear the Bandcross Flip-Flop (Block F), (U25 pin 15).

U26B pin 9 is used to stop the sweep, or keep it stopped when it has already been stopped by a sweep event. The sweep is stopped when the signal is LOW.

#### STOP SWEEP CONTROL M

The sweep can be stopped by any of the following:

- 1. The Bandcross signal (LBX) applied to Ul2B pin 5 from the Sweep Event Detection (Block  $\mathbf{F}$ ).

- 2. The Bandcross signal (LBX) applied to U12B pin 5 when driven LOW by the Sweep Generator board. (NOTE: This will only occur if the Marker Bandcross board fails to stop the sweep before it gets to 12 volts.)

- 3. The Sweep Trigger (Block L, Ul2B pin 4) is told to stop by the processor.

- 4. The Low Stop Sweep (LSSP) BNC on the rear panel is held LOW.

The Low Stop Sweep (LSSP) is an IN/OUT signal. As an input signal, LSSP is applied to Ul2C pin 9 and is used to generate HSP. As an output signal, it is taken from Ul3A pin 1 which is an open collector line pulled up to +5V.

The HSP signal goes to all devices in the instrument that need to respond to the sweep starting and stopping.

#### CRT Z-AXIS CONTROL N

The Z-AXIS signal is normally used to drive the Z-axis input of a CRT display. When this signal is 0 volts, the display will turn its beam on with normal brightness. When it is at +5 volts, the display turns its beam off (ie. blanks). When it is at -5 volts, the display intensifies its beam. The 8340A Z-AXIS signal may be used to turn the display off for bandcrossings, when the sweep is being reset (sweeper retrace), or at other times when the instrument is waiting for a sweep to start. Z-AXIS is also used to show markers by brightening the display. During all other times the Z-AXIS output is at 0 volts.

U21 is a TTL NOR gate. The outputs (U21C and U21D) are pulled up to +5 volts in the high state by R37 and R38. U21B is used to provide Op Amp U14 with a LOW TTL reference voltage. U21D pin 13 is LOW when either HSP or ZON is high. This output is connected thru R19 to Op Amp U14 that will put 0 volts on the NEG BLANK (negative blanking) output. When both HSP and ZON are low, U21D pin 13 will be HIGH and the NEG BLANK output will be at -5 Volts. When U21 pins 10 and 13 are both LOW the Z-AXIS will be 0 Volts. When pin 10 is HIGH and pin 13 is LOW Z-AXIS should be -5 Volts. Pins 10 and 13 should never both be HIGH in normal operation. When pin 10 is LOW and pin 13 is HIGH, Z-AXIS should be +5 Volts. VR1, VR2, and VR3 provide protection against a DC voltage that might be applied to the output connector. C23 and C24 provide frequency compensation to keep the Op amps stable.

#### INTERFACE SIGNALS

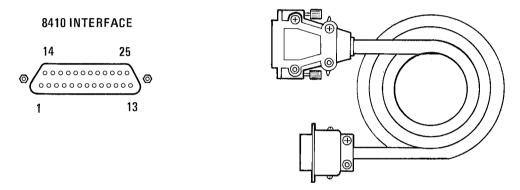

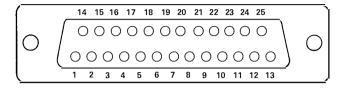

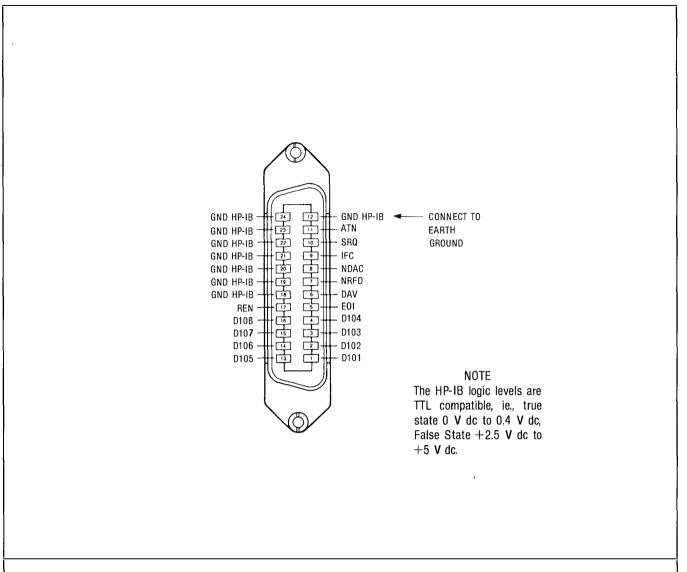

- 1. 8410B INTERFACE: The following signals from this board are needed when the 8340A is connected to the 8410B:

- a. 0-to-10v SWEEP (Drives the X-axis of the Display)

- b. STOP SWP (Allows the 8410B/C to stop the Sweep)

- c. NEG BLANK (Does Display blanking)

- d. Z-AXIS (Used to generate markers on the Display)

- e. 8410 EXT TRIG (Used to initiate 8410B/C to phase-lock every time the 8340 phase-locks i.e., new CW frequency or start of sweep.)

- 2. 8755C INTERFACE: The following signals from this board are needed when the 8340A is connected to the 8755C and it is desired to use ALTERNATE SWEEP:

- a. 0-to-10V SWEEP (Drives the X-axis on a Display)

- b. Z-AXIS (Controls Blanking and Marker generation)

- c. LALTEN (Low indicates Alternate Mode Enabled)

- d. LALTSEL (Low indicates Alternate State Active)

- e. LRETRACE (Low indicates Retrace used to synchronize with the start of sweep)

#### 3. PLOTTER INTERFACE:

- a. MUTE bar (Used to freeze the servo for Bandcrossings)

- b. PEN LIFT (Used to raise the pen for retrace and, optionally, for bandcrossings)

- c. 0-to-10V SWEEP (Used to drive the X-axis)

#### A57 MARKER BANDCROSS ASSEMBLY, TROUBLESHOOTING

#### CHECKING MICROPROCESSOR I/O ADDRESS STROBES

U28 (Block K) is connected to the I/O address bus and generates all of the I/O strobes used on this assembly. The strobes on the output of U28 can be checked using the front panel to write directly to U28's I/O address while monitoring the IC's outputs. This would be done as follows: Press [INSTR PRESET], then [MANUAL] sweep key. Connect a Logic probe to the output that is to be checked. At the front panel, enter the corresponding I/O address. The I/O address is written on the lines connected to the output of U28. For example, the WRITE RAM signal is marked, 12,R0:. The number 12 is called the CHANNEL and the number 0 is called the SUBCHANNEL. This is entered in the front panel as follows: [SHIFT] [GHz] [1] [2] [Hz] - setting the I/O channel and [SHIFT] [MHz] [0] [Hz] - setting the I/O subchannel. Once this has been done, Press [SHIFT] [KHz]. Make entries by pressing the step keys, using the RPG or by making data pad entries. Each entry will cause the WRITE RAM strobe to be generated. This will be a LOW True signal, approximately 500 ns wide, that can be monitored with the logic probe. It can also be seen on a storage scope. Refer to "Direct I/O Addressing" in Section VIII, Service Introduction, for more informaion.

#### CHECKING MICROPROCESSOR OUTPUT DEVICES

The following devices are microprocessor output devices: Ul, Ul0, U8, U16, U18, U25, U9, U17 and U23. These can be checked by using the front panel to write directly to the I/O addresses as described above. To do this, the I/O channel and subchannel must be entered at the front panel. These numbers can be found by reading the I/O address from the schematic on the write input of the device. After the address has been entered, Press [SHIFT] [KHz]. Entries can now be made directly to the device you are interested in. Monitor the outputs at the same time you enter numbers that will affect the signals of interest. For example, if the signal of interest is taken from DB2 of the I/O data bus, enter the number 0 and observe the register output; it should go LOW. Then enter the number 4 and observe that DB2 goes High. Note that if U8 and U16 are being checked, the outputs are only valid during the time the write strobe is LOW. Note that the instrument should be in MANUAL sweep mode so that the normal operation of the instrument does not cause the devices being tested to be written into.

#### CHECKING MICROPROCESSOR INPUT DEVICES

Input devices can be checked in a similar manner as the output devices. The front panel is used to set up the I/O channel and subchannel as before. U24, U8, and U16 are the only input devices on this assembly. After setting the correct address on the front panel, press [SHIFT] [Hz]. Each time [Hz] is pressed, the instrument will read from the addressed I/O device and display the results in the entry display in both decimal and octal formats. By shorting each input of the input devices to +5v or ground, each input can be checked.

#### **VERIFICATION**

#### Power On Checks

When the 8340A goes through Power On or Instrument Preset, the Marker Bandcross board is partially checked out. The instrument processor uses the circuitry in Blocks A, B, C, and K to verify the I/O data bus. This is done by sending data to the Sweep Event Memory (Block B) and then reading it back. In this manner, it can determine if any of the 16 data bits are open or shorted. If the Instrument Check light II goes off following Power On or Instrument Preset, this indicates that the above test has passed.

If the light is on, a problem is indicated. Further information about the problem can be obtained by decoding the 16 self test LEDs on the processor board. (Refer to the A60 Processor board documentation). When the Marker Bandcross board is removed from the instrument, the front panel Instrument Check light II should go on indicating that this test has failed.

#### Isolating the Problem

To help verify that the problem is on the A57 MARKER/BANDCROSS board, it may be usefull to remove the A57 assembly and observe the instrument behavior. With A57 removed, the following should occur:

- Following Power ON or Instrument Preset, Instrument Check light II should stay on and instrument Check light I should go off. All 16 self test LEDs on the processor board should remain on.

- 2. When sweeping, the sweep should stop at 12 volts before resetting. NOTE: the sweep will not be measurable at the front or rear panel connectors since the buffers for these signals are on the A57 board which has been removed. The sweep can be checked on the A58 Sweep Generator.

- The instrument should lock up properly in CW or MANUAL and perform normally except for the absence of sweep output and display blanking.

- 4. In a multi band sweep, bandcrossings will all occur when the sweep gets to 12 volts instead of the correct places.

#### SWEEP DETECTION CIRCUITS: (Blocks A through F)

#### Verification of Blocks A Through F

Press the following controls: [INSTR PRESET] [SWEEP TIME] [2] [0] [SEC] [SHIFT] [M2]. Observe the left most front panel display. This should indicate the band number as the instrument goes from band to band. Observe that the green SWEEP LED goes out at band crossings. If the numbers are not changing, this indicates that LBX (Block F) is not being generated. If the numbers seem to rapidly count from 1 through 5, this indicates that LBX (Block F) is not being pulled LOW as it should when the sweep progresses. LBX is the main output of the SWEEP DETECTION circuits.

#### Troubleshooting Blocks A Through F

Once deterimined that the problem is in Blocks  $\bf A$  through  $\bf F$ , perform the following tests:

#### Block D:

- 1. Press the following keys: [INSTR PRESET] [delta F] [1] [Mz] [SWEEP TIME] [1] [0] [sec].

- 2. Verify that U3 pin 16 has a 10 second 0-to-10V ramp present.

- 3. Check the B9 through B0 inputs of DAC U3 for the following: (B9) 1 1 1 1 1 0 1 0 0 0 (B0).

- 4. U3 pin 15 should be below 0 volts until the sweep gets to 10 volts. As the sweep rises above 10 volts, the voltage at pin 15 should rise above 0 volts, and comparator U6 should fire, forcing CMP (U6 pin 7) HIGH for about 50 ms.

#### Block E:

- 1. Press the following keys: [INSTR PRESET] [delta F] [1] [MHz].

- 2. Trigger a scope on the rising edge of CMP (U6 pin 7) and observe that U5B should have a 700 ns positive pulse at pin 5 and an inverted identical pulse at pin 12.

- 3. Observe that each time U5B fires, U5A should also fire, creating a 5.7 us positive pulse at U5A pin 13.

- 4. Make sure that U5B pin 11 is not stuck LOW. It should only go LOW when the 8340A is not sweeping.

#### Block F:

- 1. Press the following Keys: [INSTR PRESET] [START FREQ] [1] [GHz] [STOP FREQ] [1] [3] [GHz] [SWEEP TIME] [1] [0] [0] [msec] [M1] [8] [GHz] [M2] [1] [1] [GHz] [MKR delta].

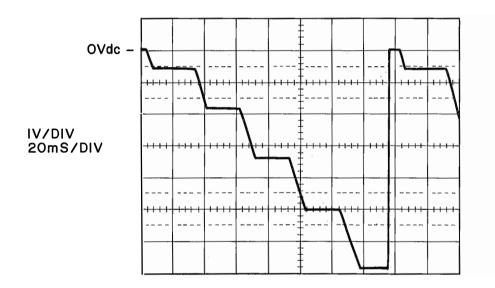

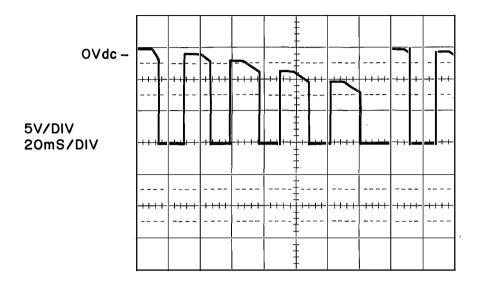

- 2. UllB pin 9 MKR should be a HIGH for 30 ms, then LOW for about 100 ms repetitively.

- 3. UllA pin 5 should go HIGH for about 50 ms when the SWEEP OUT TP5 gets to about 4 volts. When the SWEEP OUT gets to 10 volts, there should be another 50 ms pulse.

- 4. UllA pin 1 should have a single 500 ns pulse applied by U25 at the end of each sweep. If not present, check U25 (Block L) using direct I/O addressing. Refer to the direct I/O addressing description in the Service Introduction.

#### Block C:

Bi-directional buffers U8 and U16 are thoroughly verified by the Instrument Preset/Power On tests. If Instrument Check Led II is off, the buffers are good. Use direct I/O addressing to verify that data can be sent from DBO-DB15 to BO-B15. To verify the other direction from BO-B15 to DBO-DB15, do the following:

1. Press [INSTR PRESET] then [SINGLE] SWEEP. Do a read from

address 12,R2: (reads sweep event from RAM). Press [SHIFT]

[GHz], enter address [1] [2] and press any terminator (i.e.,

[GHz], [MHz], [kHz], [Hz]), press [SHIFT] [MHz], enter

subchannel [2], press any terminator, press [SHIFT] [Hz]

(read).

#### NOTE

Pressing [SHIFT] [XTAL] will cause the 8340A to pause at the next band crossing. Pressing [SHIFT] [Hz] may read a different value. Then press [SHIFT] [INT] to advance to the next band crossing and [SHIFT] [Hz] to read.

2. The entry display should show an octal number and its decimal

equivalent. Convert the octal number to binary. This is the number that should be setting on B0 through B15. It is important to realize that in order for B0 through B15 to be correct, the SWEEP EVENT MEMORY must have been properly loaded with this number. This loading is done through U8 and U16. It is therefore necessary to first check to see if U8 and U16 can transfer data from the instrument Data Bus to the Marker Bandcross Bus (B0 through B15). Before Replacing U8 or U16, verify that the two I/O strobes 12,R2: and 12,R0 are being generated by U29 (Block K). If the problem only involves a few bits, the self test leds on the A60 Processor board can be used to indicate which bits are incorrect. If all leds are on, this indicates that the problem may have to do with Blocks A, B, E, or K.

#### Block A:

- Do the following: Press [INSTR PRESET], [SINGLE] SWEEP, [SHIFT] [XTAL], [SHIFT] [GHz], enter [1] [2] and press any terminator, [SHIFT] [MHz], enter [3] and press any terminator, [SHIFT] [KHz] (write), enter [0] and press [Hz]. This should Clear Ul and UlO. Verify that lines AO through A6 are LOW.

- 2. Enter the numbers [1], [2], [4], [8], [1] [6], [3] [2], [6] [4], using the front panel. These entries should be latched into Ul and UlO and appear on the AO through A6 lines. For example, when the number 16 has been entered, the A bus should be (A6) 0 0 1 0 0 0 (A0).

- 3. Press [0] [Hz] [SHIFT] [MHz] [0] [Hz]. The A Bus should be all LOW. Note that each time a [STEP] key is pressed, the number on the A Bus should be incremented by 1. The numbers should be 0 = (A6) 0 0 0 0 0 0 0 (A0); 32 = (A6) 0 1 0 0 0 0 0 (A0); 15 = (A6) 0 0 0 1 1 1 1 (A0). U29B pin 5 should be HIGH throughout this entire test. U29B pin 6 should follow U29B pin 4.

#### Block B:

Use direct I/O addressing to check that the READ/WRITE RAM BUFFER (Block C) is able to place data on the B-BUS (B0 through Bl5). Use this Test for Block A to verify that the A-BUS can be controlled properly. Make sure that U8 and U16 can read the B-Bus as follows:

Press [INSTR PRESET], [SINGLE] SWEEP, [SHIFT] [GHz], enter [1] [2] and press any terminator, press [SHIFT] [MHz], enter [2] and press any terminator, press [SHIFT] [Hz] to read, then [SHIFT] [MHz] [2] [SHIFT] [Hz].

- 2. Alternately short each B-BUS line to + 5V and ground. After each short is made, press [SHIFT] [Hz], and note that the octal number in the entry display should indicate the appropriate bit forced HIGH for shorts to +5V, and LOW for shorts to ground.

- 3. In the above check, if all pass, it should be possible to store and read back numbers in the SWEEP EVENT RAM by doing the following:

Press [INSTR PRESET] [SHIFT] [XTAL] [SHIFT] [SINGLE] SWEEP [SHIFT] [GHz] [1] [2] [Hz]

Locations in RAM can now be written as follows:

Press [SHIFT] [MHz] [3] [Hz] [SHIFT] [kHz] to write then:

[a] [a] [Hz] (aaa = RAM address from 0 through 127)

Then press [SHIFT] [MHz] [0] [Hz] [SHIFT] [kHz] to write then:

[d] [d] [Hz] (ddd = data to be written to RAM)

It is only necessary to check through address 15. Use the above commands to write into RAM a sequece of numbers. Then verify that the numbers are properly stored in the RAM by pressing:

[SHIFT] [MHz] [3] [Hz] [SHIFT] [kHz] [a] [a] [Hz] [SHIFT] [MHz] [2] [Hz] [SHIFT] [Hz]

Note: aaa is the RAM address. The read data from the RAM will be displayed in decimal and octal in the entry display. Verify that it matches the sequence of numbers entered.

#### VERIFICATION AND TROUBLESHOOTING OF BLOCKS G THROUGH N

The Manual Sweep DAC (Block G) and the Sweep Outputs (Block H) can be checked simply by putting the front panel in MANUAL and while monitoring the sweep outputs on the front or rear panel turn the rotary control and observe that the voltage is 10 volts when the MANUAL frequency is as high as possible and that it is 0 volts when the frequency is adjusted as low as possible. It should be continuously variable in between. Note: for this test to work, the MKR RAMP must be at 0 volts. This should always be the case in MANUAL sweep.

The Sweep Trigger (Block L) can be checked from the front panel. Press [INSTR PRESET] and observe the green SWEEP LED. It should

be on during the sweep and go out momentarly for each bandcrossing and for the end of sweep. Press the EXT (external) Trigger button, make sure there is no external trigger signal, and observe that the sweep stops. Then use a logic pulser or other means to create a single external trigger. Verify that the instrument makes a complete sweep but does not continue to sweep. To check the line trigger, select [delta F] and enter [1] [MHz] so the instrument will be able to make 10 ms sweeps. Observe that the sweep repitition rate is slower when in [LINE] trigger.

The Sweep Event Detection circuitry can be verified by making the following set up:

## [INSTR PRESET] [START] [3] [GHz] [STOP] [6] [GHz] [M1] [4] [GHz] [M2] [5] [GHz] [MKR delta] [1]

Monitor the Sweep Output and the Z-axis signal on a scope. The Sweep Output should stop at 10 volts before being reset for the next sweep. If the sweep goes to 12 volts, something is wrong. Observe the Z-axis signal to see if the [MKR delta] is on for the middle portion of the sweep. Now turn off the Delta Marker and observe if two markers are indicated by the Z-axis signal. U6 pin 7 should have a pulse on it for each sweep event. If this does not occur, slow down the sweep to 200 sec and turn all markers off. Measure the inputs of U3 to see if the binary number that is input is correct. It should be 1000 decimal or in binary it should be: (bit 10) 1 1 1 1 1 0 1 0 0 0 (bit 0). This number represents a 10V set point for the comparator.

The Ram Data Unstable Timer (Block E) should be checked for the 5.7 us and 200 ns pulse widths. Make this check by clocking a scope on the CMP signal (Block D, U6 pin 7). The instrument should be in Instrument Preset state.

If U2 and U15 are suspected, A0 through A6 can be checked via DSA using the I/O data test found with the A60 Processor documentation. If these signatures are incorrect, make sure that the Ram Data Unstable Timer (Block  $\mathbf{E}$ ) is not clocking the Address Register. This should be disabled by putting the instrument in MANUAL sweep while performing the test.

A57 Marker/Bandcross P1 Pin I/O (1 of 3)

| Pin      | Mnemonic               | Levels                                        | Source                              | Destination            |  |  |

|----------|------------------------|-----------------------------------------------|-------------------------------------|------------------------|--|--|

| 1<br>56  | GND PLANE<br>GND PLANE | 0V<br>0V                                      | INSTRUMENT GROUND INSTRUMENT GROUND | *0<br>*0               |  |  |

| 2<br>57  | HMRKR<br>LINE TRIG     | TTL (HIGH TRUE)<br>LINE FREQ 7 TO 10 <b>V</b> | J<br>A62-CR1 CATHODE/A62R1          | XA26P1-43<br>L         |  |  |

| 3<br>58  | LRETRACE               | TTL (LOW TRUE)                                | J                                   | F A62J31-11, 25        |  |  |

| 4<br>59  | LALTSEL                | TTL (LOW TRUE)                                | J                                   | A62J31-10, 24          |  |  |

| 5<br>60  | LALTEN                 | TTL (LOW TRUE)                                | J                                   | A62J31-9, 23           |  |  |

| 6<br>61  | MUTE                   | TTL (HIGH TRUE)                               | J                                   | A62J31-8, 22           |  |  |

| 7<br>62  | 8410 TRIG              | ΠL                                            | J                                   | A62J31-7               |  |  |

| 8<br>63  |                        |                                               |                                     |                        |  |  |

| 9<br>64  |                        |                                               |                                     |                        |  |  |

| 10<br>65 |                        |                                               |                                     |                        |  |  |

| 11<br>66 |                        |                                               |                                     |                        |  |  |

| 12<br>67 | HMRKR                  | TTL (HIGH TRUE)                               | J .                                 | XA26P1-43              |  |  |

| 13<br>68 | HSP<br>LINE TRIG       | TTL (HIGH TRUE)<br>LINE FREQ 7 TO 10 <b>V</b> | M<br>A62-CR1 CATHDDE/A62R1          | *I N<br>L              |  |  |

| 14<br>69 | LIPS<br>LBX            | TTL (LOW TRUE)<br>TTL (LOW TRUE)              | XA52P1-36/A62J1-19<br>*F            | *NOT USED<br>M XA59-69 |  |  |

| 15<br>70 | SIDA<br>GND PLANE      | TTL (LOW TRUE)<br>OV                          | XA60P1-15<br>INSTRUMENT GROUND      | *K<br>*0               |  |  |

| 16<br>71 | SIOB<br>GND PLANE      | TTL (LOW TRUE)<br>OV                          | XA60P1-16<br>INSTRUMENT GROUND      | *NOT USED<br>*O        |  |  |

| 17<br>72 | ADRO<br>GND PLANE      | TTL<br>OV                                     | XA60P1-17<br>INSTRUMENT GROUND      | *K<br>*0               |  |  |

| 18<br>73 | ADR2<br>ADR1           | TTL<br>TTL                                    | XA60P1-18<br>XA60P1-73              | *K<br>*K               |  |  |

| 19<br>74 | ADR4<br>ADR3           | ΠL<br>ΠL                                      | XA60P1-19<br>XA60P1-74              | *K                     |  |  |

A single letter in the source or destination column refers to a function block on this assembly schematic.

An asterick (\*) denotes multiple sources or destinations; refer to the A62 Motherboard Wiring List for a complete representation of signal sources and destinations.

A57 Marker/Bandcross P1 Pin I/O (2 of 3)

| Pin      | Mnemonic     | Levels | Source                              | Destination |  |  |

|----------|--------------|--------|-------------------------------------|-------------|--|--|

| 20       | DB0          | TTL    | *C XA60P1-20                        | *A C G J    |  |  |

| 75       | GND PLANE    | 0V     | INSTRUMENT GROUND                   | *O          |  |  |

| 21       | DB2          | TTL    | *C XA60P1-21                        | *A C G J    |  |  |

| 76       | DB1          | TTL    | *C XA60P1-76                        | *A C G J    |  |  |

| 22       | DB4          | TTL    | *C XA60P1-22                        | *A C G J    |  |  |

|          | DB3          | TTL    | *C XA60P1-77                        | *A C G J    |  |  |

| 23       | DB6          | TTL    | *C XA60P1-23                        | *A C G J    |  |  |

| 78       | DB5          | TTL    | *C XA60P1-78                        | *A C G J    |  |  |

| 24       | DB8          | TTL    | *C XA60P1-24                        | *C G        |  |  |

| 79       | DB7          | TTL    | *C XA60P1-79                        | *C G J      |  |  |

| 25       | DB10         | TTL    | *C   XA60P1-25                      | *C L        |  |  |

| 80       | DB9          | TTL    | *C XA60P1-80                        | *C G        |  |  |

| 26       | DB12         | TTL    | .*C   XA60P1-26                     | *C L        |  |  |

| 81       | DB11         | TTL    | *C   XA60P1-81                      | *C L        |  |  |

| 27       | DB14         | TTL    | *C   XA60P1-27                      | *C L        |  |  |

| 82       | DB13         | TTL    | *C   XA60P1-82                      | *C L        |  |  |

| 28       | DB15         | TTL    | *C   XA60P1-83                      | *C L        |  |  |

| 29       | GND PLANE    | 0V     | INSTRUMENT GROUND INSTRUMENT GROUND | *0          |  |  |

| 84       | GND PLANE    | 0V     |                                     | *0          |  |  |

| 30       | GND PLANE    | OV     | INSTRUMENT GROUND INSTRUMENT GROUND | *0          |  |  |

| 85       | GND PLANE    | OV     |                                     | *0          |  |  |

| 31       | GND PLANE    | 0V     | INSTRUMENT GROUND INSTRUMENT GROUND | *0          |  |  |

| 86       | GND PLANE    | 0V     |                                     | *0          |  |  |

| 32<br>87 |              |        |                                     |             |  |  |

| 33<br>88 |              |        |                                     |             |  |  |

| 34       | GND PLANE    | OV     | INSTRUMENT GROUND INSTRUMENT GROUND | *0          |  |  |

| 89       | GND PLANE    | OV     |                                     | *0          |  |  |

| 35       | +20√         | +20V   | XA52P1-16, 40                       | *0          |  |  |

| 90       | +20 <b>V</b> | +20V   | XA52P1-16, 40                       | *0          |  |  |

| 36       | +5.2V        | +5.2V  | XA52P1-17, 18, 41, 42               | *0          |  |  |

| 91       | +12V         | +12V   | XA52P1-9, 33                        | *NOT USED   |  |  |

| 37       | +5.2V        | +5.2V  | XA52P1-17, 18, 41, 42               | *0          |  |  |

| 92       | +5.2V        | +5.2V  | XA52P1-17, 18, 41, 42               | *0          |  |  |

A single letter in the source or destination column refers to a function block on this assembly schematic.

An asterick (\*) denotes multiple sources or destinations; refer to the A62 Motherboard Wiring List for a complete representation of signal sources and destinations.

A57 Marker/Bandcross P1 Pin I/O (3 of 3)

| Pin       | Mnemonic               | Levels                             | Source                                         | Destination               |  |  |

|-----------|------------------------|------------------------------------|------------------------------------------------|---------------------------|--|--|

| 38        | ─15V<br>─5.2V          | −15V<br>−5.2V                      | XA56P1-15, 30<br>XA53P1-18, 36                 | *0                        |  |  |

| 39<br>94  | −10V<br>  −10V         | −10V<br>−10V                       | XA53P1-12, 13, 31, 32<br>XA53P1-12, 13, 31, 32 | *NOT USED ·<br>*NOT USED  |  |  |

| 40<br>95  | GND PLANE              | OV                                 | INSTRUMENT GROUND                              | *0                        |  |  |

| 41<br>96  | NEG BLANK<br>MKR RMP   | 0, +5V<br>0 TO 10V SWEEP           | N<br>XA58P1-96                                 | A62J31-1, 15<br>D G       |  |  |

| 42<br>97  | RFSWP<br>Z-AXIS BLANK  | 10V/SWEEP<br>+5V/-5V               | H<br>N                                         | XA27P1-17<br>A62J31-2, 16 |  |  |

| 43<br>98  | FPNLSWP                | 10V/SWEEP                          | Н                                              | A62J9-SMC CENTER          |  |  |

| 44<br>99  | RPNLSWP<br>FPNLSWP RTN | 10V/SWEEP<br>0V                    | H<br>H                                         | A62J8-SMC CENTER          |  |  |

| 45<br>100 | RGND<br>RPNLSWP RTN    | 0V<br>0V                           | STAR GND POINT<br>H                            | *0<br>*                   |  |  |

| 46<br>101 | RGND<br>RGND           | 0V<br>0V                           | STAR GND POINT<br>STAR GND POINT               | *0<br>*0                  |  |  |

| 47<br>102 |                        |                                    |                                                |                           |  |  |

| 48<br>103 |                        |                                    |                                                |                           |  |  |

| 49<br>104 | HULH<br>HULH           | TTL (HIGH TRUE)<br>TTL (HIGH TRUE) | A62J19-16<br>A62J19-16                         | *NOT USED<br>*NOT USED    |  |  |

| 50<br>105 | HRFON .                | TTL (HIGH TRUE)                    | J                                              | *                         |  |  |

| 51<br>106 | EXT TRIG               | EXTERNAL SOURCE LEVEL              | A62J31-4, 18                                   | L A62J31-4, 18            |  |  |

| 52<br>107 | LSSP                   | TTL (LOW TRUE)                     | M                                              | A62J31-5, 19              |  |  |

| 53<br>108 | PEN LIFT               | CLAMP AT 56V                       | J                                              | A62J31-6, 20              |  |  |

| 54<br>109 | LSRQ<br>PEN LIFT RTN   | TTL (LOW TRUE)<br>OV               | *<br>J                                         | *NOT USED<br>A62J31-21    |  |  |

| 55<br>110 | GND PLANE<br>GND PLANE | 0V<br>0V                           | INSTRUMENT GROUND                              | *0<br>*0                  |  |  |

A single letter in the source or destination column refers to a function block on this assembly schematic.

An asterick (\*) denotes multiple sources or destinations; refer to the A62 Motherboard Wiring List for a complete representation of signal sources and destinations.

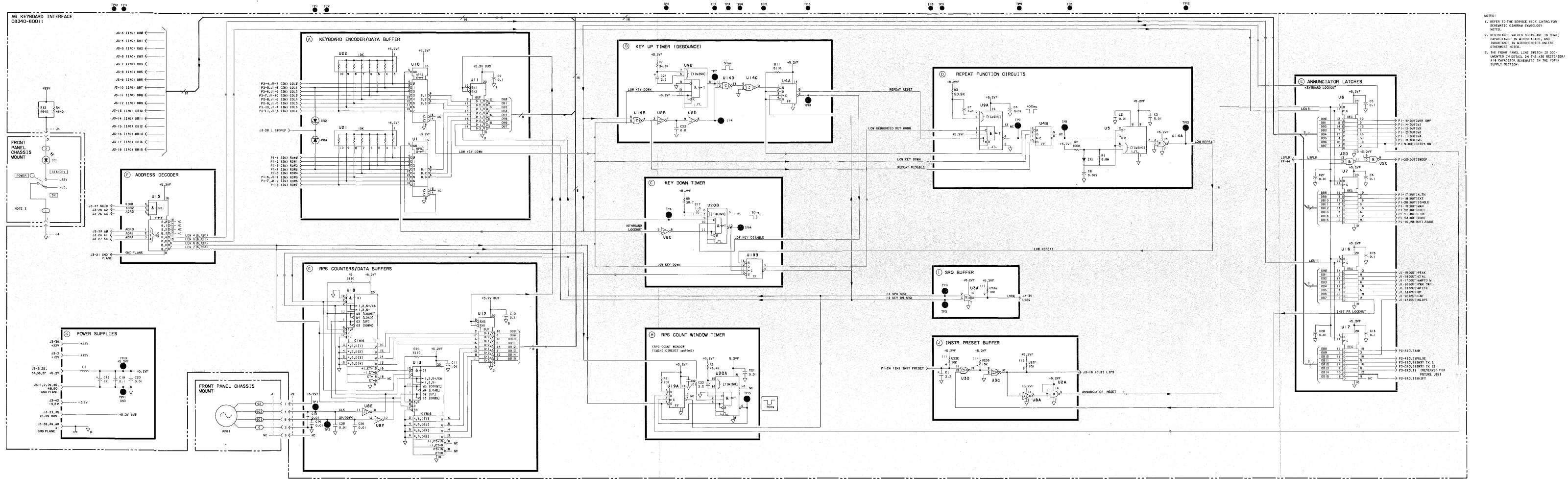

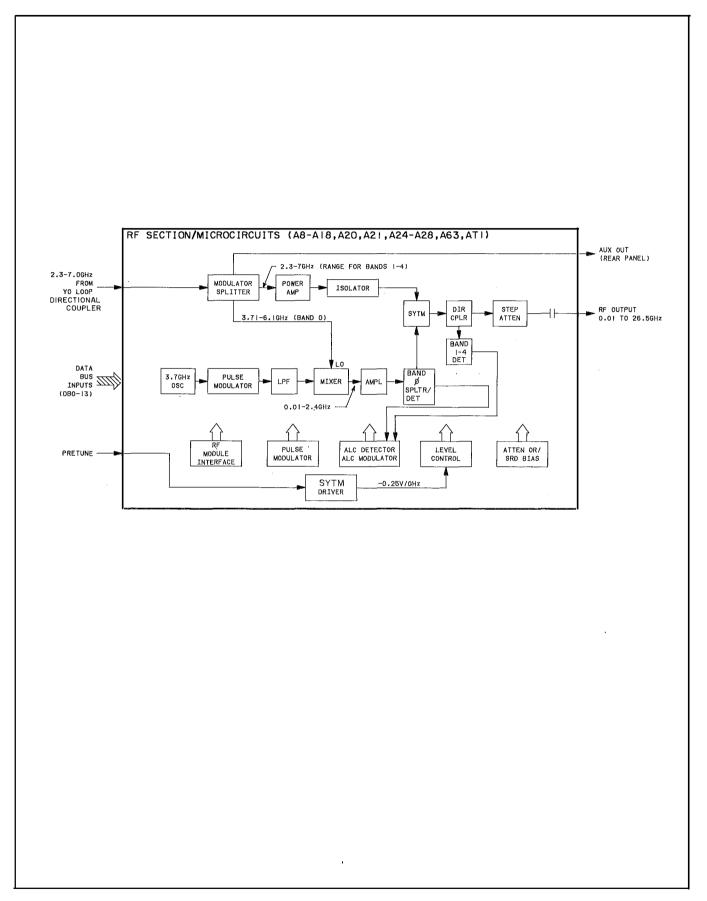

Figure 8G-4. A57 Marker/Bandcross, Schematic Diagram

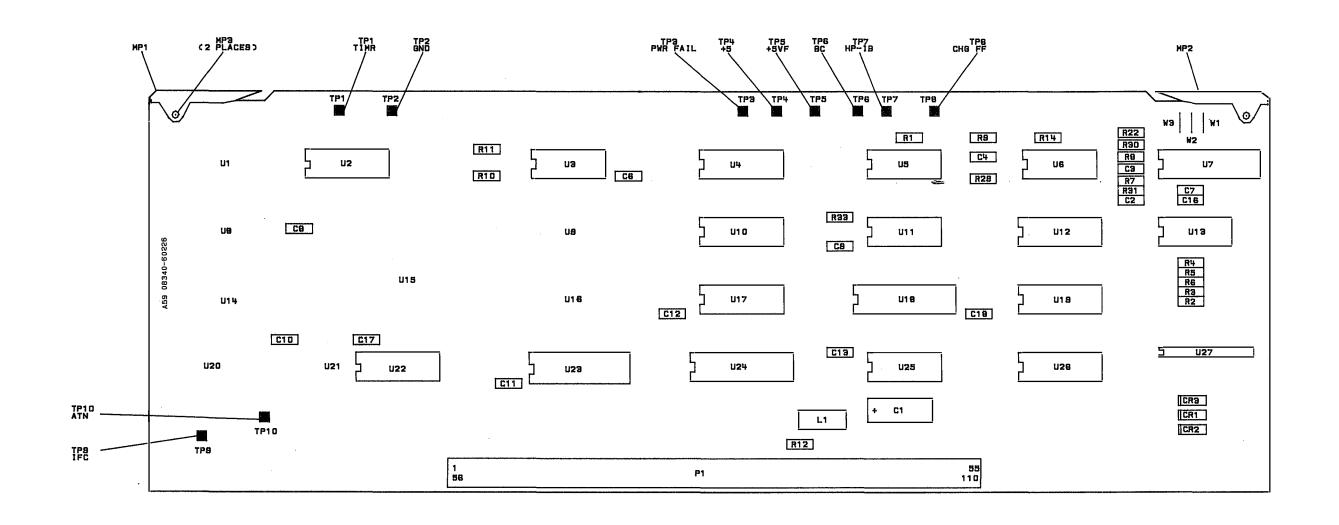

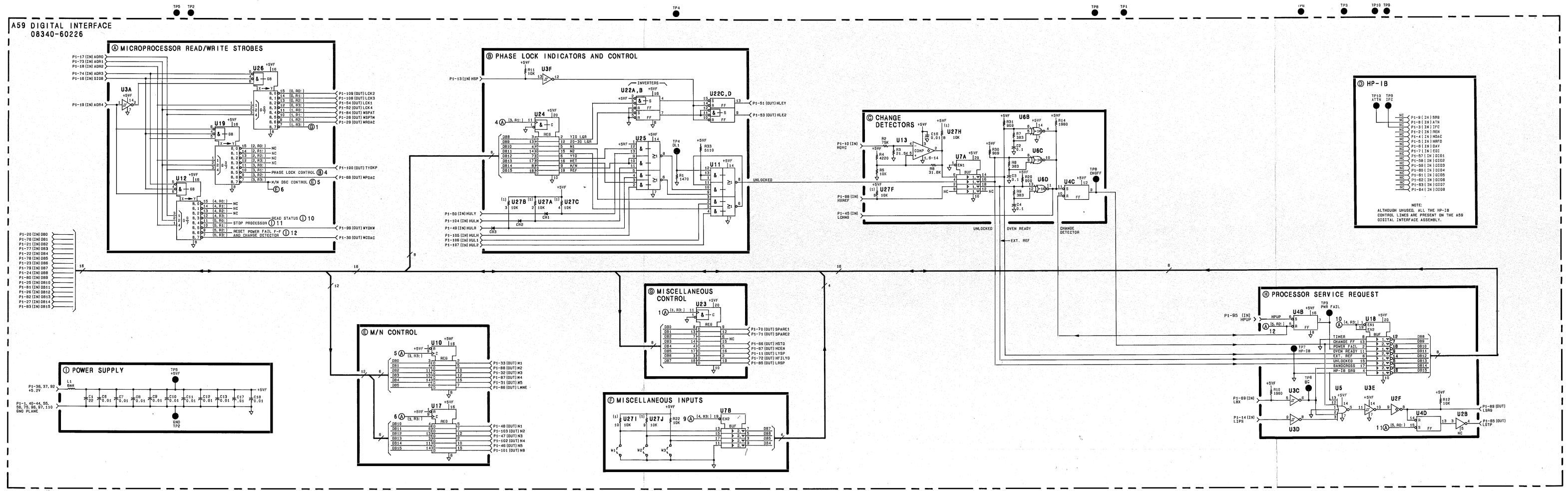

## A59 DIGITAL INTERFACE ASSEMBLY, CIRCUIT DESCRIPTION

#### INTRODUCTION

The Digital Interface board communicates to the Microprocessor the tasks which need to be performed. In normal operation of the instrument, the Microprocessor stops running when all tasks are completed. This control (when the processor runs) is done via the LSTP (Low STop Processor) control line (Block H). Many I/O addresses are decoded on the board that are used to latch data from the I/O data bus for several assemblies that are external to this board. Some signals are latched on the A59 Digital Interface and then sent to other assemblies via the motherboard. An example is Block E.

Phase Lock Indicators and Control (Block B) also reside on the board.

#### MICROPROCESSOR READ/WRITE STROBES A

The three decoders (U12, U19, and U26) decode 24 possible I/O addresses. The outputs of these 3-to-8 line decoders are used by circuits both on and off the A59 board to clock latches connected to the I/O bus or to enable buffers connected to the bus for input operations. There are also several decoders on other PC boards where additional addresses are decoded. SIOB is a 500 ns pulse which enables the three decoders. While they are enabled, the logic signals on ADRO through ADR4 are used to select specific I/O addresses. For example, I/O address 3,R3: (Channel 3, Subchannel 3) causes a 500 ns strobe at U19 pin 7 when lines ADR4 through ADRO are (ADR4) 0 1 1 1 1 (ADRO) and at the same time SIOB is LOW.

#### PHASE LOCK INDICATORS AND CONTROL B

The six Phase-lock loops in the instrument can be monitored to determine if they are locked by writing into the U24 register a mask that will select individual Lock Indicator signals and allow the processor to test them via U18 Processor Service Request circuits (Block H). During instrument operation, the instrument processor sends data to U24 register that sets up U25 and U11 to monitor the Phase Lock Indicators. These indicate either a locked or unlocked condition for a particular 8340A function. The outputs of U24, pins 2 and 12, are inverted by U22A and U22B. U22A and U22B are RS flip-flops wired as inverters. These inverted signals are used to set flip-flops U22C and U22D. The outputs of these flip-flops control the LOCK/ROLL signals for the 20-30 Loop and the YO Loop. Once these flip-flops are set, the corresponding phase-lock loop will try to lock. This condition will persist until the set signals are removed and the High Sweep signal (HSP)

goes True indicating the start of a sweep. This will cause the appropriate oscillator to switch from LOCK to ROLL mode. When the instrument is sweeping, either the YO or the 20-30 oscillator will be allowed to sweep by having its LOCK/ROLL control line set to ROLL. The 20-30 is swept when the YO Delta F is < 5 mHz. NOTE: The YO Delta F is the overall sweep width divided by the harmonic number (1 thru 4). The remaining outputs of U24 are ANDed with the corresponding Oscillator LOCKED signals and ORed together by U11 and U25 to generate the UNLOCKED signal.

The DLI (TP4) test point can be pulled to +5 Volts for troubleshooting to cause the processor to think all oscillators are locked up when they are not. This should cause the front panel UNLOCKED light to go out.

#### CHANGE DETECTOR C

Several conditions need to be continuously monitored and responded to by the Instrument Controller when they change state. Since the Controller stops running when it has completed its tasks, this circuit detects changes in instrument conditions and causes the controller to run again so that the changes can be responded to. The changes that are detected are:

- 1. OVEN becoming cold or up to temperature.

- 2. Change in enabled Phase LOCK indicators.

- 3. Rear panel frequency reference switch set to EXT.

- 4. LCHNG line being driven LOW due to one of the following conditions:

- a. Change in the OVERMODULATION indicator.

- b. Change in UNLEVELED indicator.

- c. Service request from the ADC.

When the control signal from the OVEN HOVC falls below 3.5 volts, the output of comparitor Ul3 goes HIGH. This signal is buffered by U7A which drives U6B. U6B immediately produces a LOW at pin 4 in response to the positive-going change at input pin 6. When C2 is charged up some 100 us later, pin 5 of U6B goes HIGH, forcing the exclusive OR gate to return its output to a HIGH. The resulting negative-going pulse from U6B will cause flip-flop U4C to be Set. The output of U4C goes to Block H and causes the instrument processor to check for a change in one of the conditions listed above. When the OVEN control signal changes in the opposite direction (i.e., rises above 3.5 volts), U13 will change states again. This change will again cause U6B to create a LOW-going pulse about 100 us wide. Changes in the UNLOCKED and External

Reference signals also cause LOW-going pulses on the LCHNG line. The LCHNG line runs on the A62 Motherboard so that other circuits in the instrument can indicate the need for service from the instrument controller. Where this is done an exclusive OR gate similar to U6B is also used to create LOW-going pulses on LCHNG.

#### M/N CONTROL E

Two registers, U10 and U17, are used by the processor to latch control signals necessary to program the M/N Oscillator. This is done when the processor does a WRITE to I/O address 3,R3:. The M/N off signal could be used to turn the M/N oscillator off. Currently the oscillator is never turned off.

#### MISCELLANEOUS INPUTS F

The buffer, U7B, is used to allow the processor to determine if any options are set. Currently none are used. The input on I/O bit 4 (DB4) is tied LOW and can be used by the processor to determine that the digital interface is present.

#### MISCELLANEOUS CONTROL G

The register, U23, is used by the processor to latch eight bits of information that are sent to the motherboard to control various functions. This is done when the processor does a WRITE to I/O address 1,R3:. The control signals are:

- HSTD (High STandarD) A HIGH indicates the Internal Frequency Standard has been selected. The rear panel switch should cause this signal to change state.

- HFILYO (High FILtered YO) A HIGH places a large filter capacitor acress the YO coil. This is done in the CW or MANUAL mode.

- LRSP (Low Reset SweeP) A LOW causes the Sweep Generator to reset the sweep. This is done at the end of every sweep. The reset signal is removed before the sweep starts.

- LYSP (Low YO SweeP) This signal goes to the A55 YO Driver board. It is a TTL signal that is LOW for YO sweep widths greater than 5 MHz. This signal switches out a filtering capacitor on the driver board so that it does not add any swept frequency delay.

- HCEN (High Compensation Enable) This signal goes to the A55 YO Driver board. It is a TTL signal that, when HIGH, allows the ramp voltage VCOMP to be added to PRETUNE on the driver board. This compensates for the swept frequency delay of the YO.

#### PROCESSOR SERVICE REQUESTS H

Buffer/Register U18 is used by the processor to determine which tasks need to be performed. All conditions that need the processor's attention are communicated through this register except for the front panel, which can generate its own service request. All possible reasons for service are ORed by U5 and the result is sent to the processor on the LSRQ line, indicating that service is requested. The LSTP line is driven by flip-flop U4D that is used to stop the processor from running when all tasks have been completed. U9B in an inverting open collector output buffer. Flip-flop U4D is set when the processor does a WRITE to I/O address 5,RO:. This is done to stop the processor when all pending tasks have been completed. U4D is reset to cause the controller to run again any time LSRQ is driven LOW. LSRQ can be driven LOW by U5 through U3E and U9F, or by the front panel to indicate a key has been pushed or the rotary control has been turned.

The Following conditions can be monitored when the processor does a READ from I/O address 4,R3: through U18:

- BANDCROSS This line is driven by the LBX from A57 Marker Band Cross board. After being inverted by A59U3C, A59TP6 "BC" will go HIGH whenever a sweep event occurs. The Sweep Generator can also drive the LBX line if the sweep ever excedes 13 volts.

- ☑ UNLOCKED An oscillator is unlocked

- EXT. REF. External Reference is selected by the rear panel Frequency Standard INT/EXT Switch.

- POWER FAIL This indicates that a Power On has just occured. This is used by the processor to determine whether to do an Instrument Preset or a Power On restore of the last state. The processor cannot otherwise distinguish between Power On and Instrument Preset.

#### POWER SUPPLY I

The only supply for the board is +5V. Ll and Cl through Cl8 provide required digital filtering.

#### A59 DIGITAL INTERFACE ASSEMBLY, TROUBLESHOOTING

#### CHECKING MICROPROCESSOR I/O ADDRESS STROBES (BLOCK A).

U12, U19, and U26 (Block A) are connected to the I/O address bus and generate 24 I/O strobes which are used either on this assembly or are sent via the motherboard to other assemblies. These strobes on the outputs of U12, U19, and U26 can be checked using the front panel to write directly to the I/O addresses (Direct I/O), while monitoring the outputs of the 3-to-8 line decoders. This can be done as follows: Press [INSTR] [PRESET], then [MANUAL] sweep key. Connect a logic probe to the output that is to be checked. Enter into the front panel the corresponding I/O address. The I/O address is shown on the schematic printed above the outputs of Ul2, Ul9, and U26 in the following form: m,Rn: Where "m" is called the I/O CHANNEL and "n" is the I/O SUBCHANNEL. For example, assume that we wish to test U19 pin 7. The I/O address is 3.R3: This is entered into the front panel as follows: [SHIFT] [GHz] [3] [Hz] sets the I/O channel, and [SHIFT] [MHz] [3] [Hz] sets the I/O subchannel. Pressing [SHIFT] [KHz] activates the selected I/O address. Make entries by pressing the step keys, using the RPG, or by making data pad entries. Each entry will cause the M/N Oscillator Control strope to be generated. This will be a LOW-True signal approximately 500 ns wide that can be monitored with the logic probe. It can also be seen on a storage scope.

Refer to Direct I/O Addressing in Section VIII, "Service Introduction", for more information.

#### CHECKING MICROPROCESSOR OUTPUT DEVICES (BLOCKS B, E, AND G)